8051 内核-单片机

**MA86E/L104**

**说明书**

**版本: A1.3**

This document contains information on a new product under development by Megawin. Megawin reserves the right to change or discontinue this product without notice.

© Megawin Technology Co., Ltd. 2005 All rights reserved.

2015/05 version A1.3

## 功能

- 1-T 80C51 微处理器

- **MA86E/L104 4K** 的程序存储器空间

- ISP 程序空间可以选择 0.5KB/1KB/1.5KB.....3.5KB

- 软件灵活的定义 IAP 空间大小

- 密码保护程序区访问

- Flash 写/擦 次数: 2000 次@ IAP 空间 0.5KB, 1000 次@ IAP 空间 1KB, ...

- Flash 数据保留时间: 100 年 25°C

- **MA82E/L104 出厂默认空间设置**

- ◆ AP 程序空间 (0000h~07FFh)

- ◆ IAP 数据空间 (0800h~0BFFh)

- ◆ ISP 引导码空间 (0C00h~0FFFh) (保留在线烧录用, 用户程序无法更动)

- 内部 256 字节数据存储器

- 中断控制

- 6 中断源, 4 个优先级

- 二个外部中断, nINT0 和 nINT1

- 所有的外部中断支持高/低或上升/下降沿触发

- 两个 16-位 定时/计数, Timer 0 和 Timer 1.

- T0CKO 在 P34 和 T1CKO 在 P35.

- T0/T1 可以选择 X12 模式

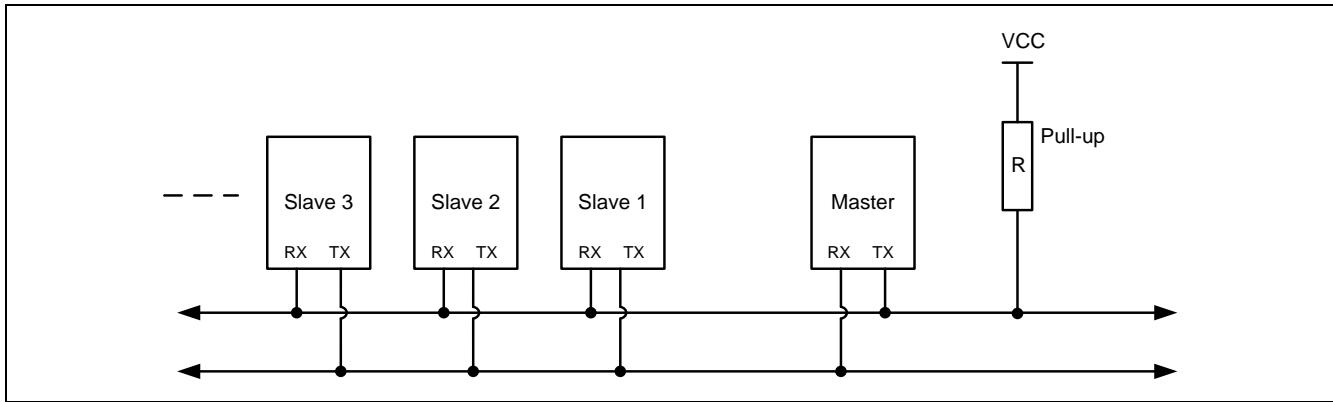

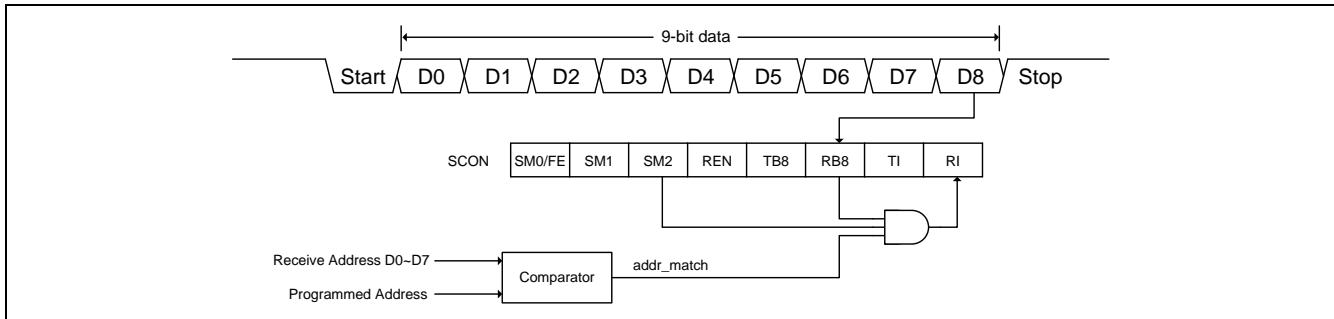

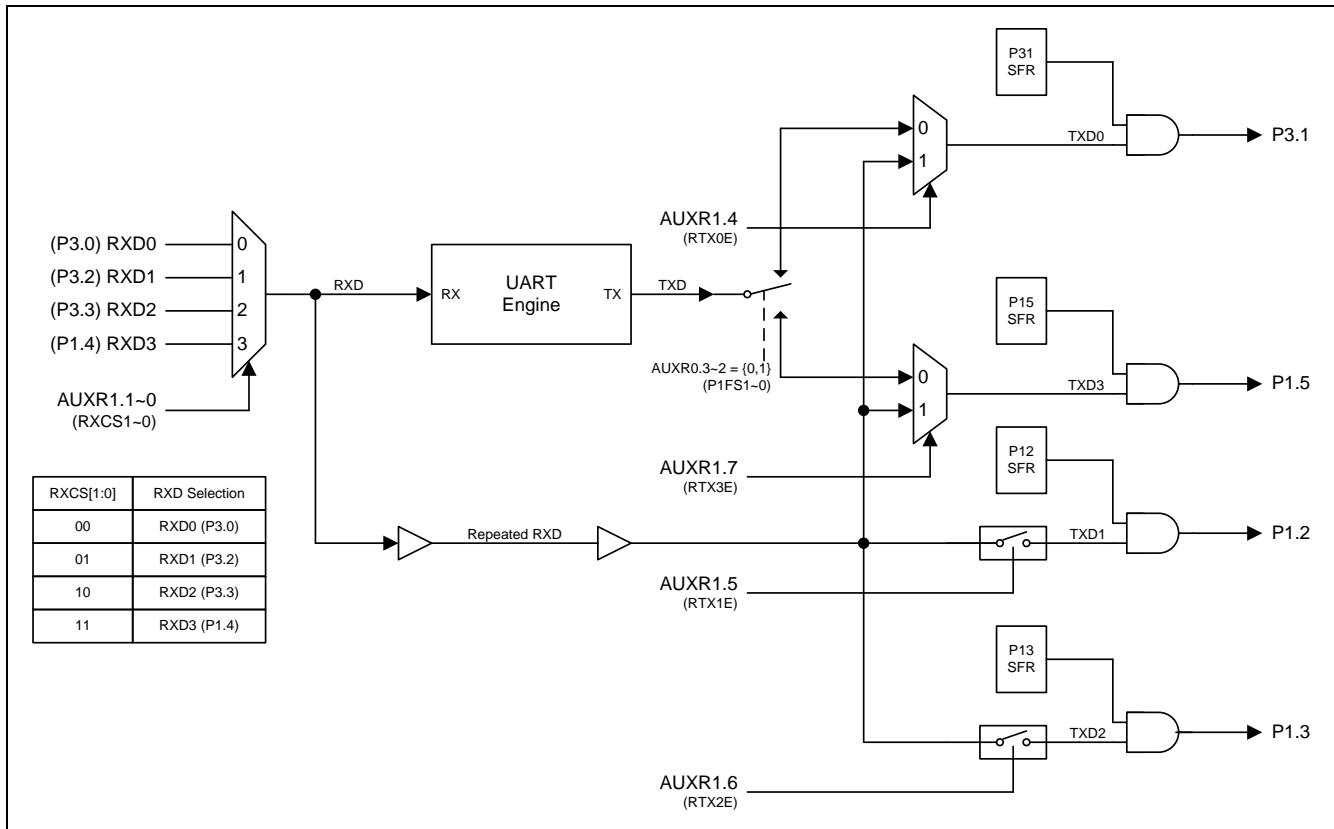

- 增强型 UART (S0)

- 帧误差侦测

- 自动地址识别

- 速度增强机制(X2/X4 模式)

- 4 通道 UART 重复机构

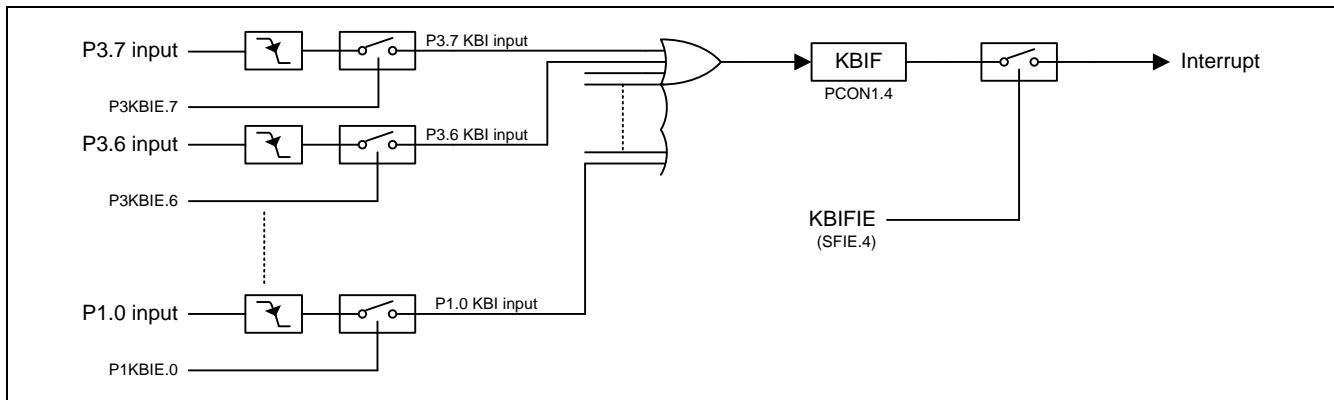

- 所有 I/O 具有键盘中断功能.

- 可程序控制的看门狗定时器, 时钟来源为 ILRCO

- 通过 CPU 或上电复位一次性使能

- 看门狗溢出会中断或复位 CPU

- 掉电模式支持看门狗功能(Watch Mode)

- 20 脚的封装片最多 18 个 I/O

- P3 可以设置准双向口模式, 推挽输出模式, 开漏集输出模式, 仅输入模式。

- P1, P4.0 和 P4.1 可以设置为推挽输出模式, 开漏集输出模式。

- P4.0, P4.1 和 P3.6 公用 XTAL2, XTAL1 和 RST.

- 所有的 I/O 有唤醒功能。

- 多种省电模式: 掉电模式, 空闲模式, 慢频模式, 副频模式, watch 模式和 monitor 模式。

- 所有的中断能唤醒空闲模式。

- 6 中断能唤醒掉电模式。

- 慢频模式和副频模式支持低速 MCU 运转

- Watch 模式在掉电模式下能复位 CPU

- Monitor 模式在掉电模式下支持 BOD0 复位 CPU (仅仅 L-系列)

- 低电压检测: VDD 4.0V E-系列 和 VDD 2.6V L-系列

- 中断 CPU 或 复位 CPU

- 在掉电模式下唤醒 CPU (仅仅 L-系列)

- 工作电压:

- MA86E104: 4.2V~5.5V, 要求 Flash 写操作 (ISP/IAP/ICP) 最小电压 4.5V

- MA86L104: 2.4V~3.6V., 要求 Flash 写操作 (ISP/IAP/ICP) 最小电压 2.7V

- 工作频率范围: 25MHz(最大)

- MA86E104: 0 – 12MHz @ 4.2V – 5.5V 和 0 – 25MHz @ 4.5V – 5.5V

- MA86L104: 0 – 12MHz @ 2.4V – 3.6V 和 0 – 25MHz @ 2.7V – 3.6V

- 时钟源种类:

- 内部震荡 22.118MHz/24MHz (IHRCO): 典型的, 工厂校对到±1%。

- 外部晶振模式

- 内部低功耗 64KHz RC 振荡(ILRCO)

- 外部时钟输入(ECKI) XTAL2/P4.0

- 内部震荡输出 XTAL2/P4.0

- 工作温度:

- 工业级 (-40°C to +85°C)\*

- 封装类型:

- SOP20: MA86E/L104AS20

- SOP16: MA86E/L104AS16

- SOP8: MA86E/L104AS8

\*:抽样检测

# 目录

|                            |    |

|----------------------------|----|

| 功能                         | 3  |

| <b>目录</b>                  | 5  |

| 1. 概述                      | 9  |

| 2. 方框图                     | 10 |

| 3. 特殊功能寄存器                 | 11 |

| 3.1. SFR 图                 | 11 |

| 3.2. SFR 位分配               | 12 |

| 3.3. 辅助 SFR 图 (Page P)     | 13 |

| 3.4. 辅助 SFR 位分配 (Page P)   | 14 |

| 4. 引脚结构                    | 15 |

| 4.1. 封装指南                  | 15 |

| 4.2. 引脚定义                  | 16 |

| 4.3. 备选功能转换                | 17 |

| 5. 8051 CPU 功能描述           | 18 |

| 5.1. CPU 寄存器               | 18 |

| 5.2. CPU 时序                | 19 |

| 5.3. CPU 寻址 模式             | 19 |

| 6. 存储器组织                   | 21 |

| 6.1. 程序存储器                 | 21 |

| 6.2. 数据存储器                 | 22 |

| 6.3. 关于 C51 编译器的声明标识符      | 24 |

| 7. 数据指针寄存器 (DPTR)          | 25 |

| 8. 系统时钟                    | 26 |

| 8.1. 时钟结构                  | 26 |

| 8.2. 时钟寄存器                 | 27 |

| 8.3. 系统时钟示例代码              | 29 |

| 9. 看门狗定时器 (WDT)            | 35 |

| 9.1. WDT 结构                | 35 |

| 9.2. WDT 在掉电模式和空闲模式期间      | 35 |

| 9.3. WDT 寄存器               | 36 |

| 9.4. WDT 硬件选项              | 38 |

| 9.5. WDT 示例代码              | 39 |

| 10. 系统复位                   | 42 |

| 10.1. 复位源                  | 42 |

| 10.2. 上电复位                 | 42 |

| 10.3. 外部复位                 | 43 |

| 10.4. 软件复位                 | 43 |

| 10.5. 掉电检测器 (Brown-Out) 复位 | 44 |

| 10.6. WDT 复位               | 44 |

| 10.7. 非法地址复位               | 44 |

|                                       |           |

|---------------------------------------|-----------|

| 10.8. 复位示例代码 .....                    | 45        |

| <b>11. 电源管理 .....</b>                 | <b>46</b> |

| 11.1. 电源监控模块 .....                    | 46        |

| 11.2. 电源节省模式 .....                    | 46        |

| 11.2.1. 慢频模式 .....                    | 46        |

| 11.2.2. 副频模式 .....                    | 46        |

| 11.2.3. Watch 模式 .....                | 47        |

| 11.2.4. Monitor 模式 (仅仅使用于 L-系列) ..... | 47        |

| 11.2.5. 空闲模式 .....                    | 47        |

| 11.2.6. 掉电模式 .....                    | 47        |

| 11.2.7. 中断唤醒掉电模式 .....                | 48        |

| 11.2.8. 复位唤醒掉电模式 .....                | 48        |

| 11.2.9. KBI 键盘唤醒掉电模式 .....            | 49        |

| 11.3. 电源控制寄存器 .....                   | 50        |

| 11.4. 电源控制示例代码 .....                  | 52        |

| <b>12. 输入输出口配置 .....</b>              | <b>60</b> |

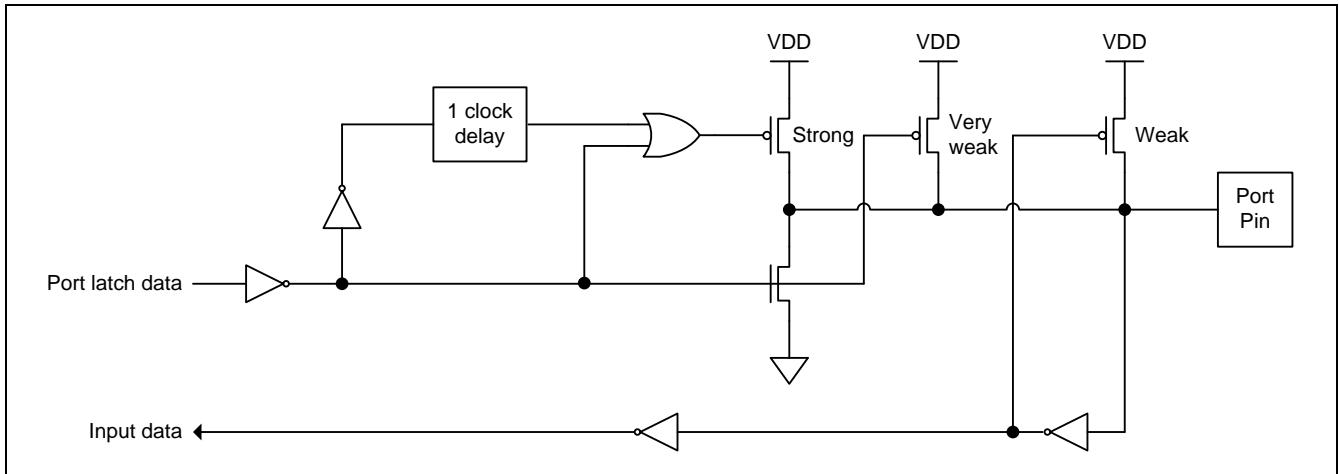

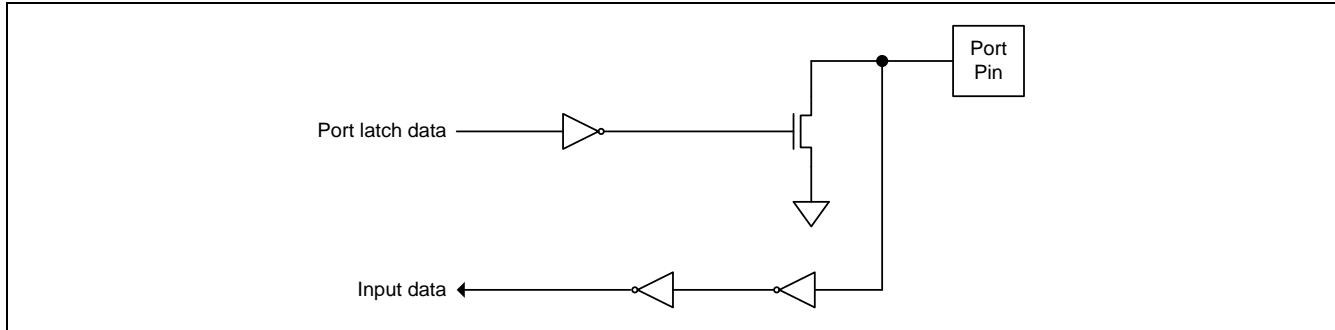

| 12.1. 输入输出口结构 .....                   | 60        |

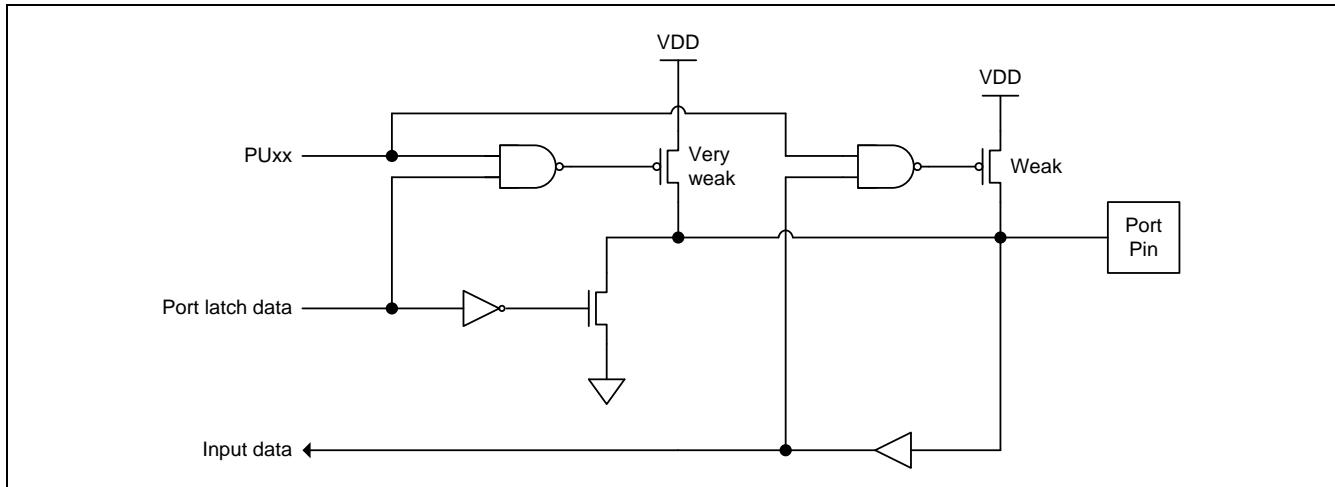

| 12.1.1. 端口 3 准双向口 .....               | 60        |

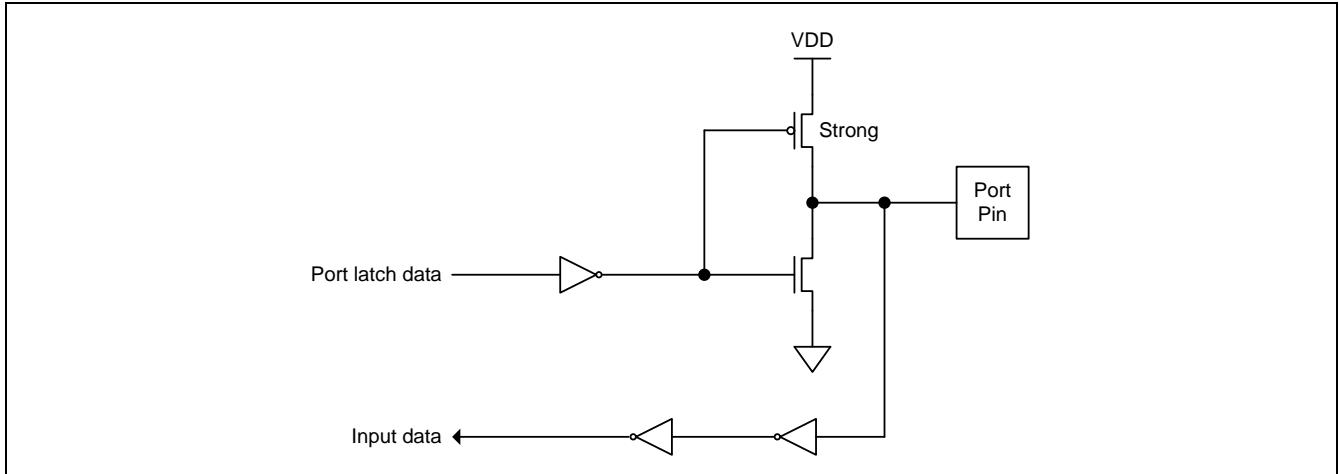

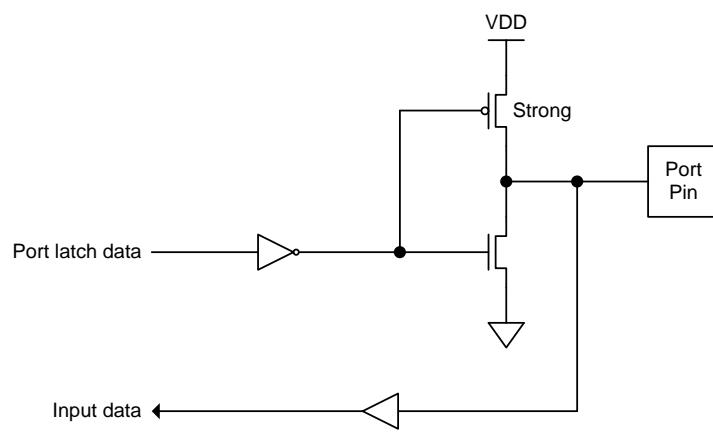

| 12.1.2. 端口 3 推挽输出 .....               | 61        |

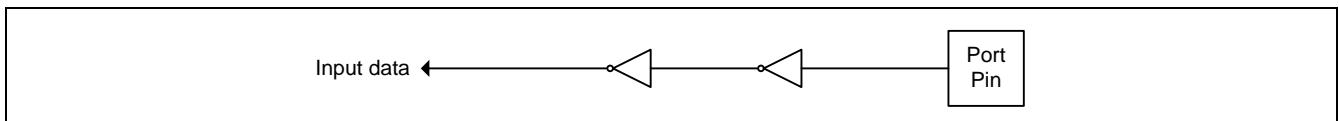

| 12.1.3. 端口 3 仅是输入 (高阻抗输入) 模式 .....    | 61        |

| 12.1.4. 端口 3 开漏输出 .....               | 62        |

| 12.1.5. 通用端口集电极开漏输出结构 .....           | 62        |

| 12.1.6. 通用端口推挽输出结构 .....              | 62        |

| 12.1.7. 通用端口输入结构 .....                | 63        |

| 12.2. 输入输出口寄存器 .....                  | 64        |

| 12.2.1. 端口 1 寄存器 .....                | 64        |

| 12.2.2. 端口 3 寄存器 .....                | 65        |

| 12.2.3. 端口 4 寄存器 .....                | 65        |

| 12.2.4. 上拉控制寄存器 .....                 | 66        |

| 12.3. GPIO 示例代码 .....                 | 67        |

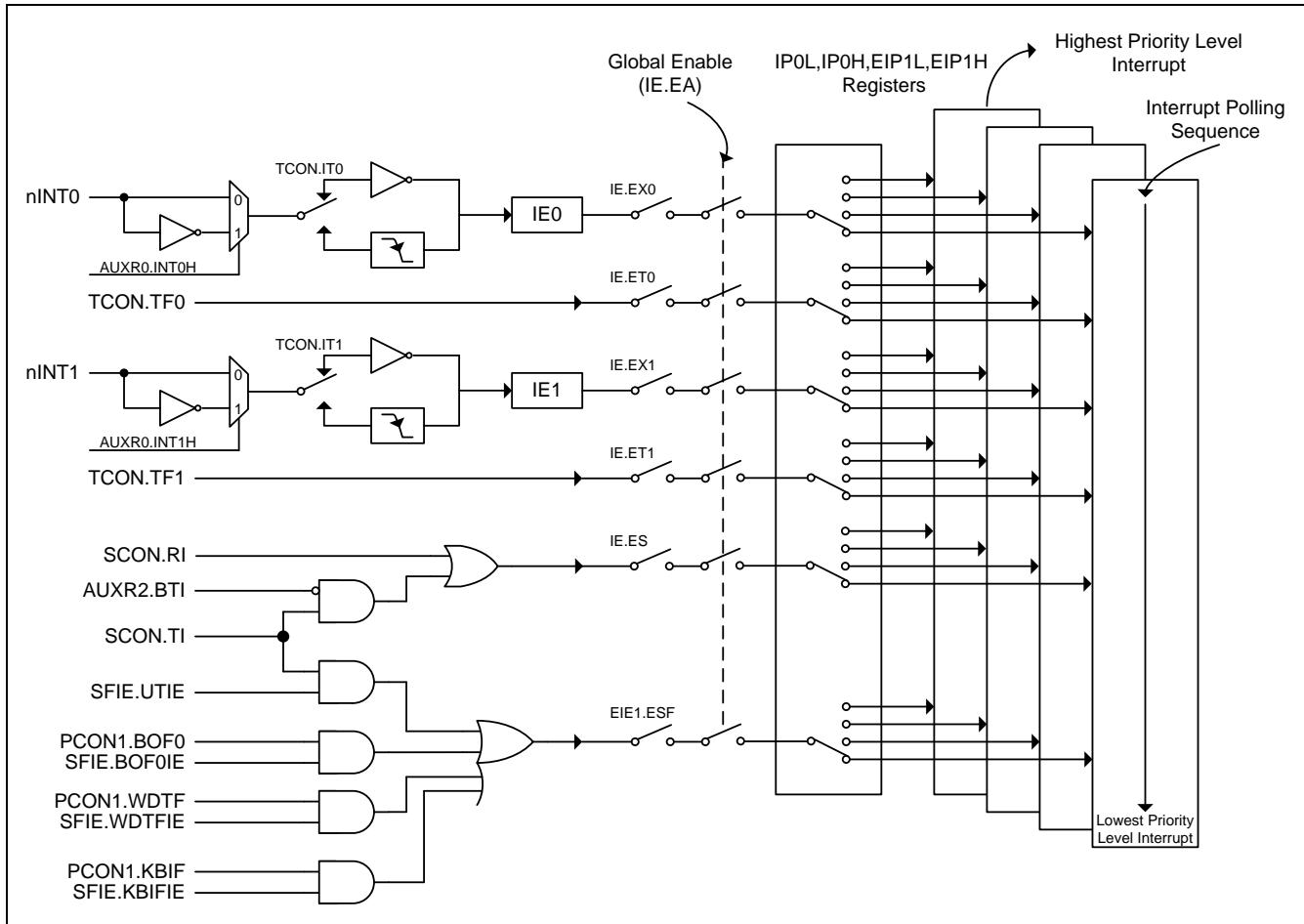

| <b>13. 中断 .....</b>                   | <b>68</b> |

| 13.1. 中断结构 .....                      | 68        |

| 13.2. 中断源 .....                       | 69        |

| 13.3. 中断使能 .....                      | 70        |

| 13.4. 中断优先级 .....                     | 70        |

| 13.5. 中断处理 .....                      | 71        |

| 13.6. TI 的特别中断向量 .....                | 71        |

| 13.7. 中断寄存器 .....                     | 72        |

| 13.8. 中断示例代码 .....                    | 76        |

| <b>14. 定时器/计数器 .....</b>              | <b>78</b> |

| 14.1. 定时器 0 和 定时器 1 .....             | 78        |

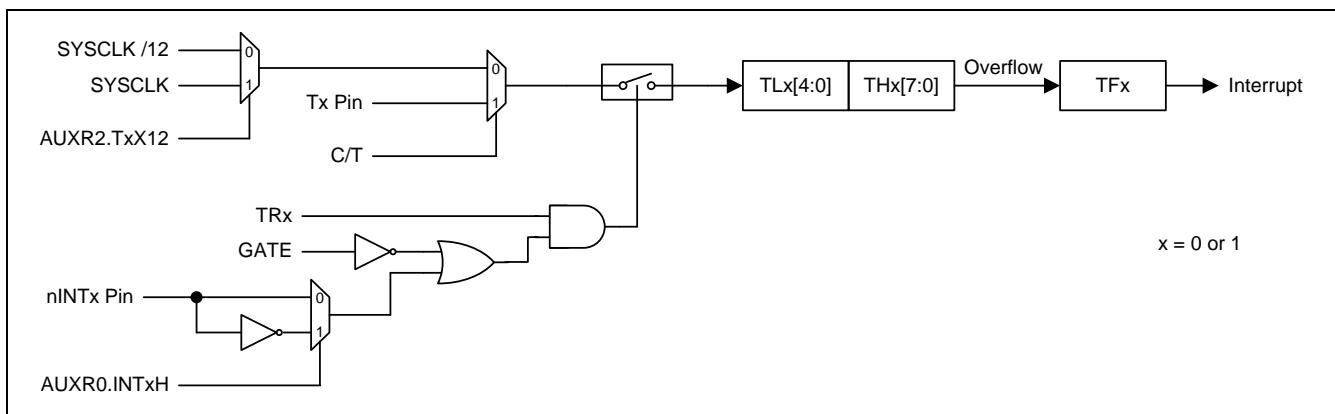

| 14.1.1. 模式 0 结构 .....                 | 78        |

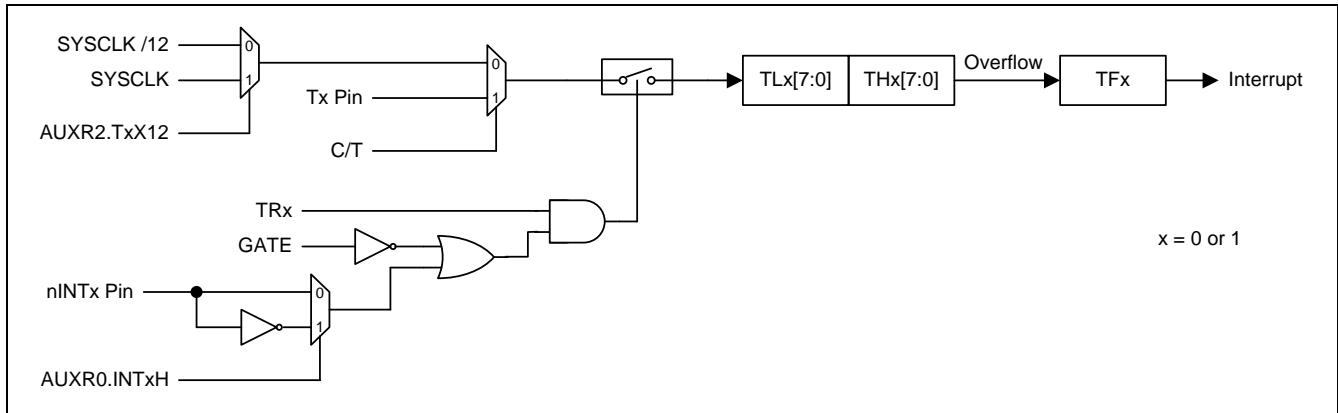

| 14.1.2. 模式 1 结构 .....                 | 79        |

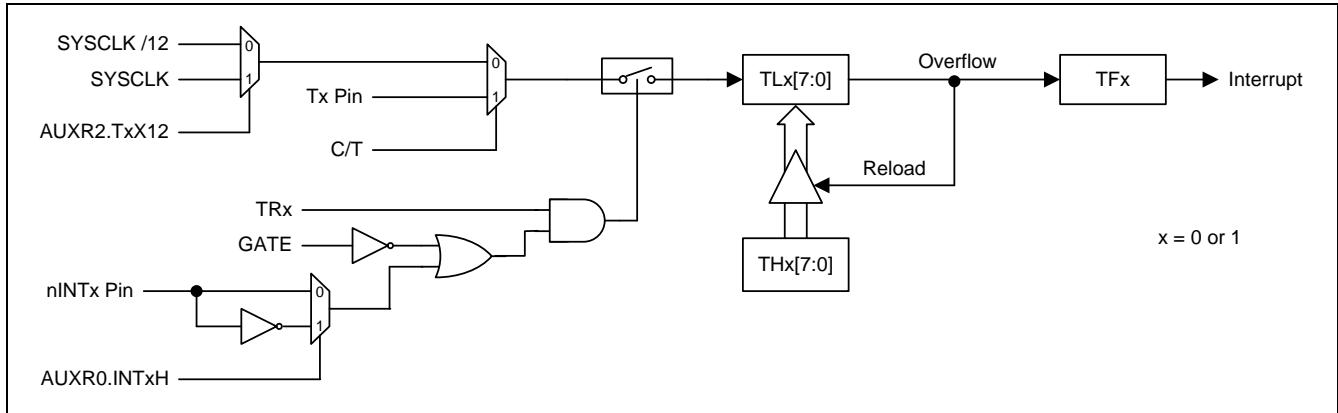

| 14.1.3. 模式 2 结构 .....                 | 79        |

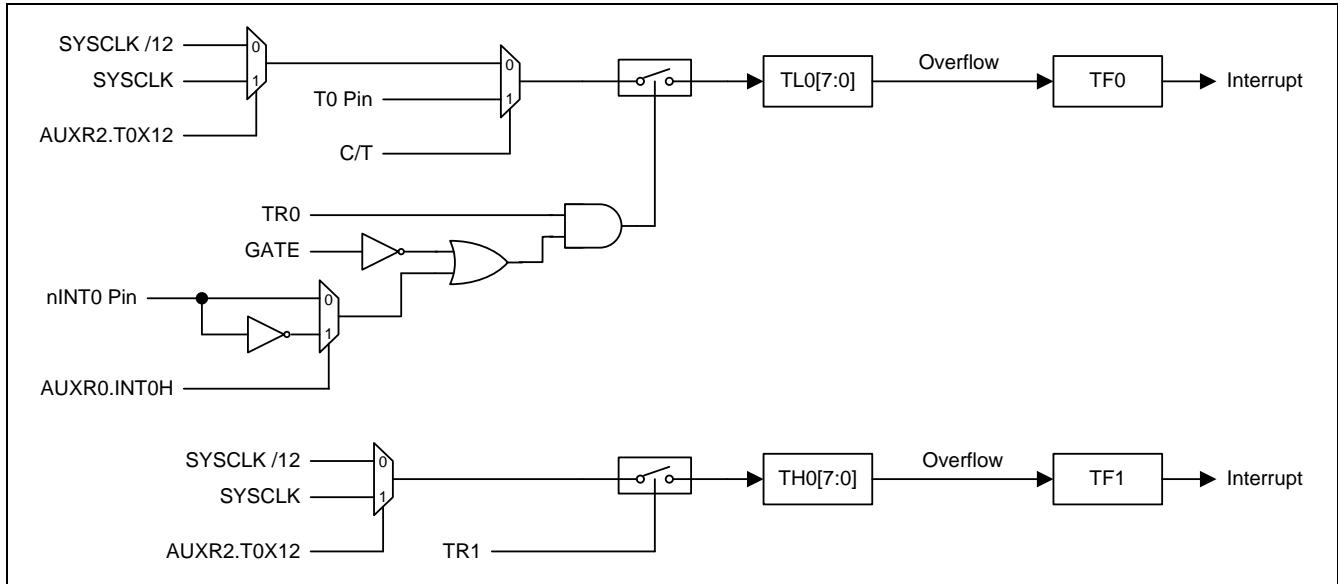

| 14.1.4. 模式 3 结构 .....                 | 80        |

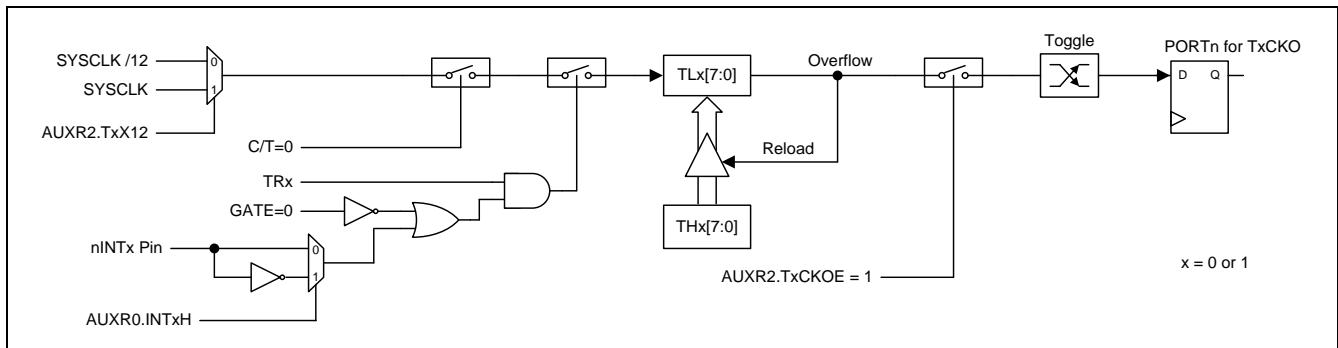

| 14.1.5. 定时器 0/1 可编程时钟输出 .....         | 80        |

|                                          |            |

|------------------------------------------|------------|

| 14.1.6. 定时器 0/1 寄存器 .....                | 82         |

| 14.1.7. 定时器 0/1 示例代码 .....               | 84         |

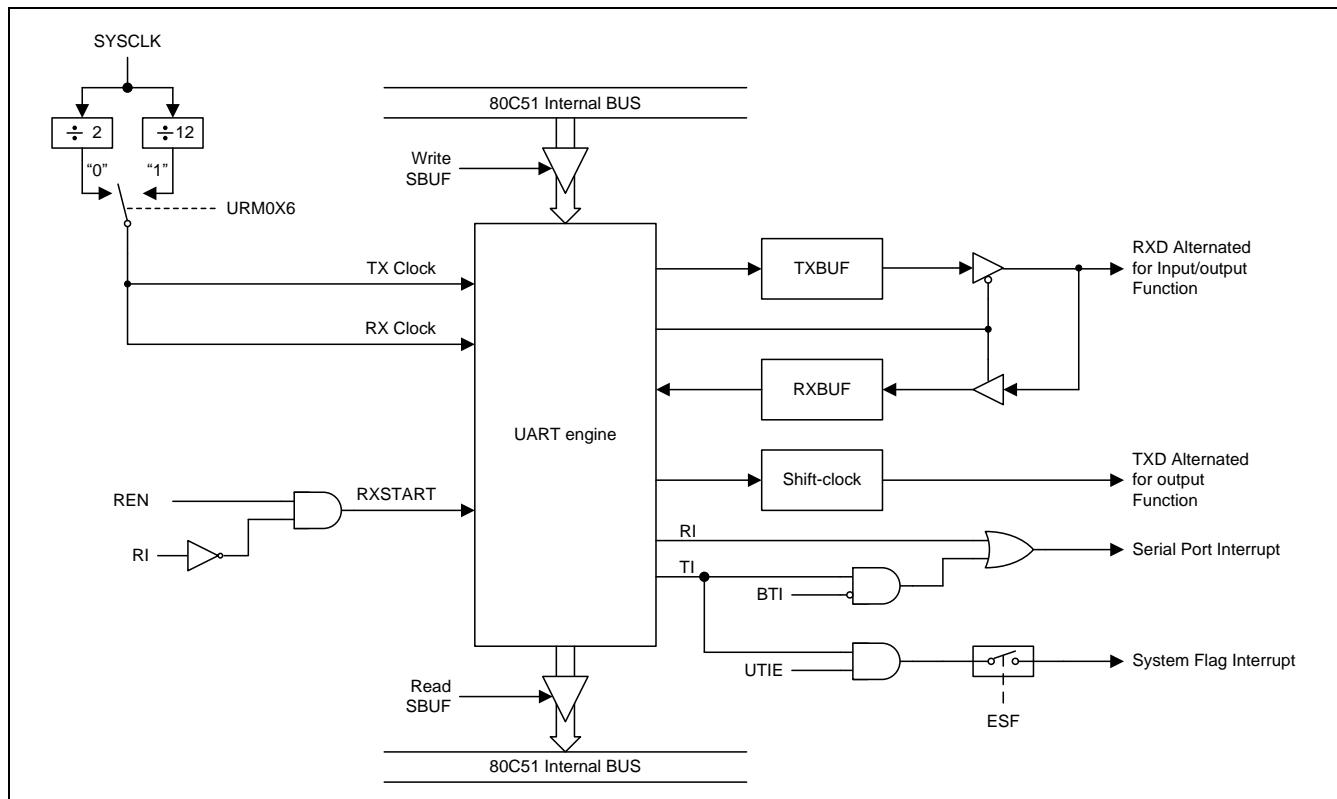

| <b>15. 串行口(UART).....</b>                | <b>89</b>  |

| 15.1. 串行口模式 0.....                       | 90         |

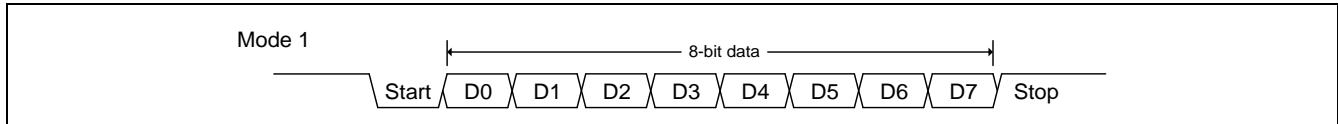

| 15.2. 串行口模式 1.....                       | 92         |

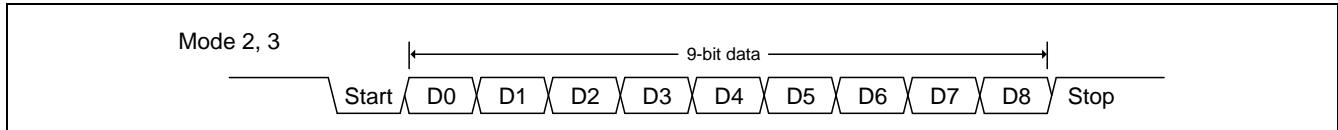

| 15.3. 串行口模式 2 和模式 3 .....                | 93         |

| 15.4. 错误帧检测.....                         | 93         |

| 15.5. 多处理器通讯 .....                       | 94         |

| 15.6. 自动地址识别 .....                       | 94         |

| 15.7. 波特率设置.....                         | 96         |

| 15.7.1. 波特率模式 0.....                     | 96         |

| 15.7.2. 波特率模式 2.....                     | 96         |

| 15.7.3. 波特率模式 1 和 3.....                 | 96         |

| 15.8. 串行口重复模式 .....                      | 100        |

| 15.9. 串行口寄存器 .....                       | 101        |

| 15.10. 串行口示例代码 .....                     | 105        |

| <b>16. 键盘中断(KBI) .....</b>               | <b>107</b> |

| 16.1. 键盘中断结构图 .....                      | 107        |

| 16.2. 键盘中断寄存器 .....                      | 107        |

| 16.3. 键盘中断示例代码 .....                     | 109        |

| <b>17. ISP and IAP .....</b>             | <b>111</b> |

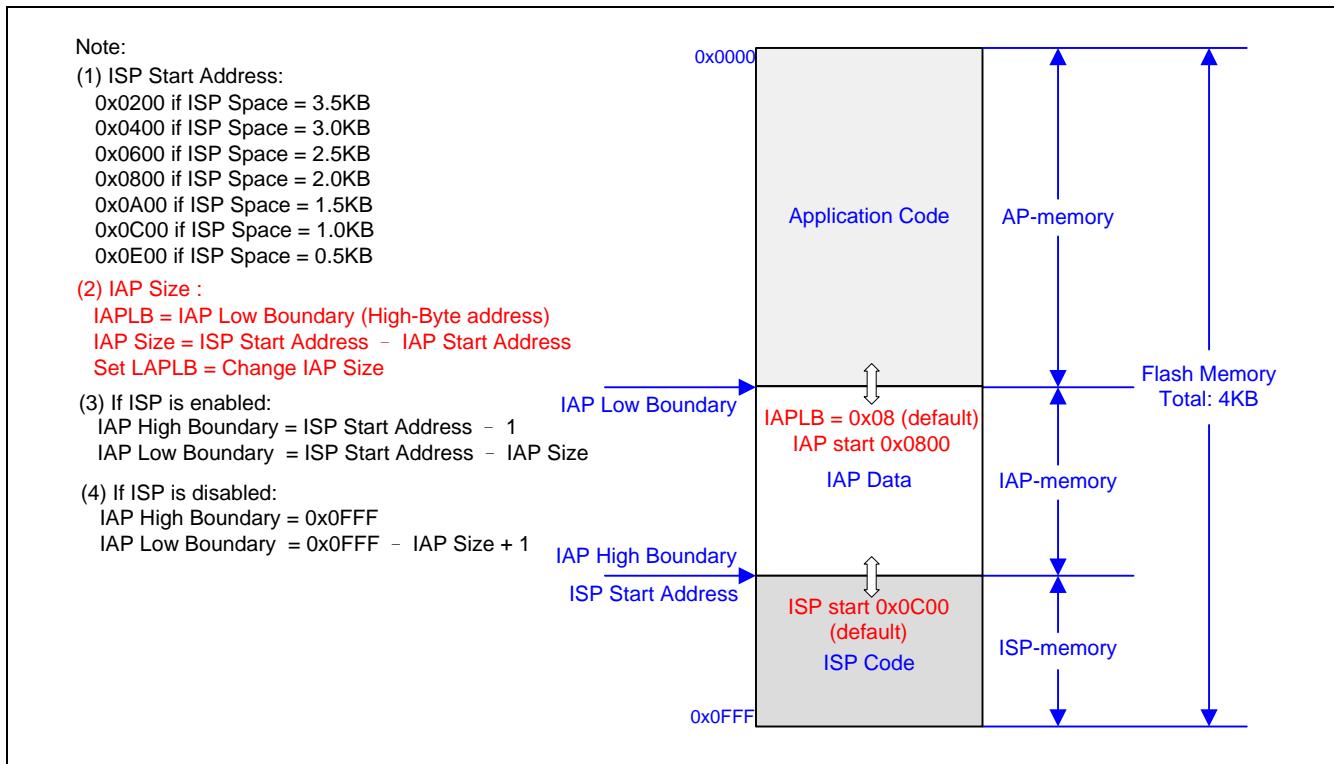

| 17.1. MA86E/L104 闪存存储配置 .....            | 111        |

| 17.2. MA86E/L104 在 ISP/IAP 访问 Flash..... | 112        |

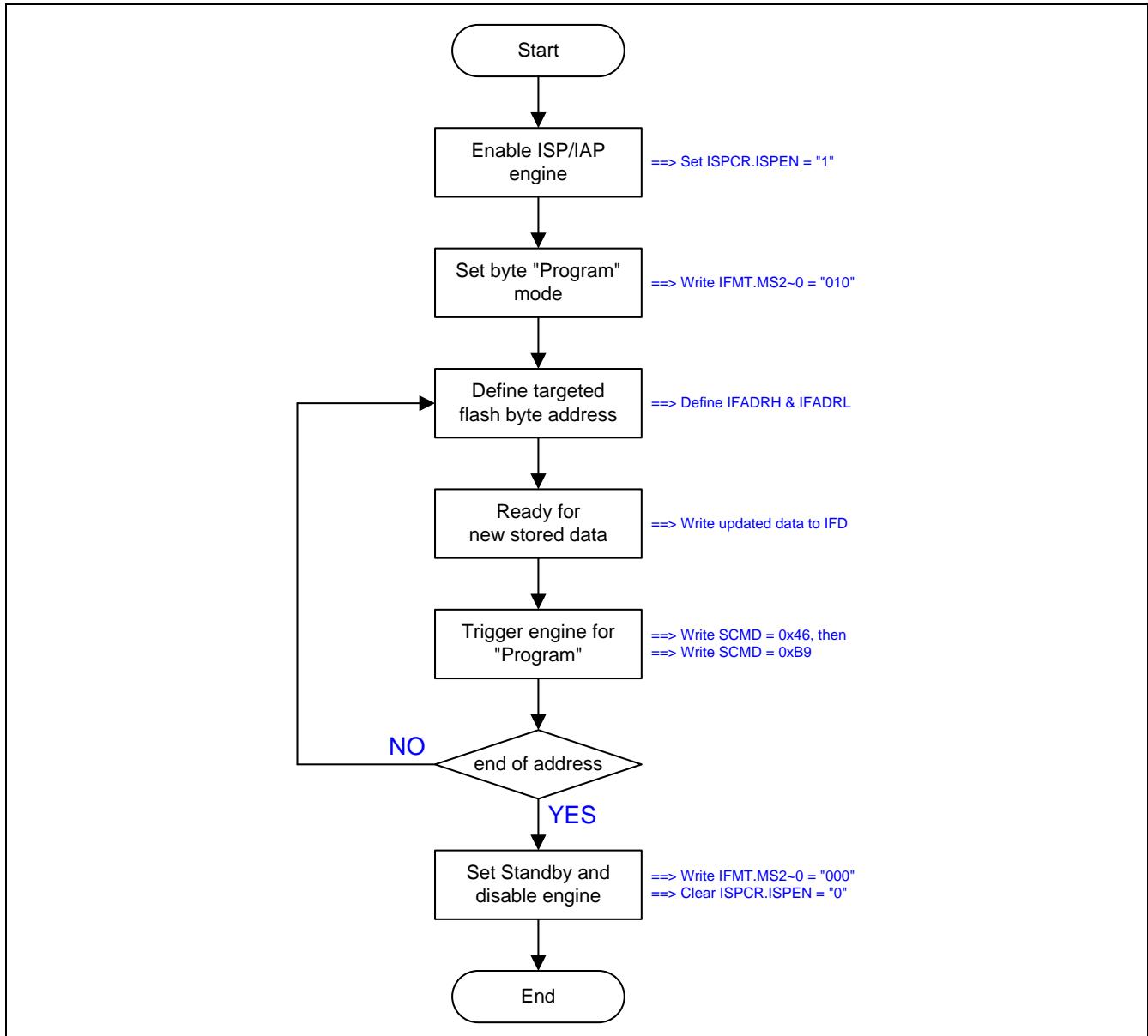

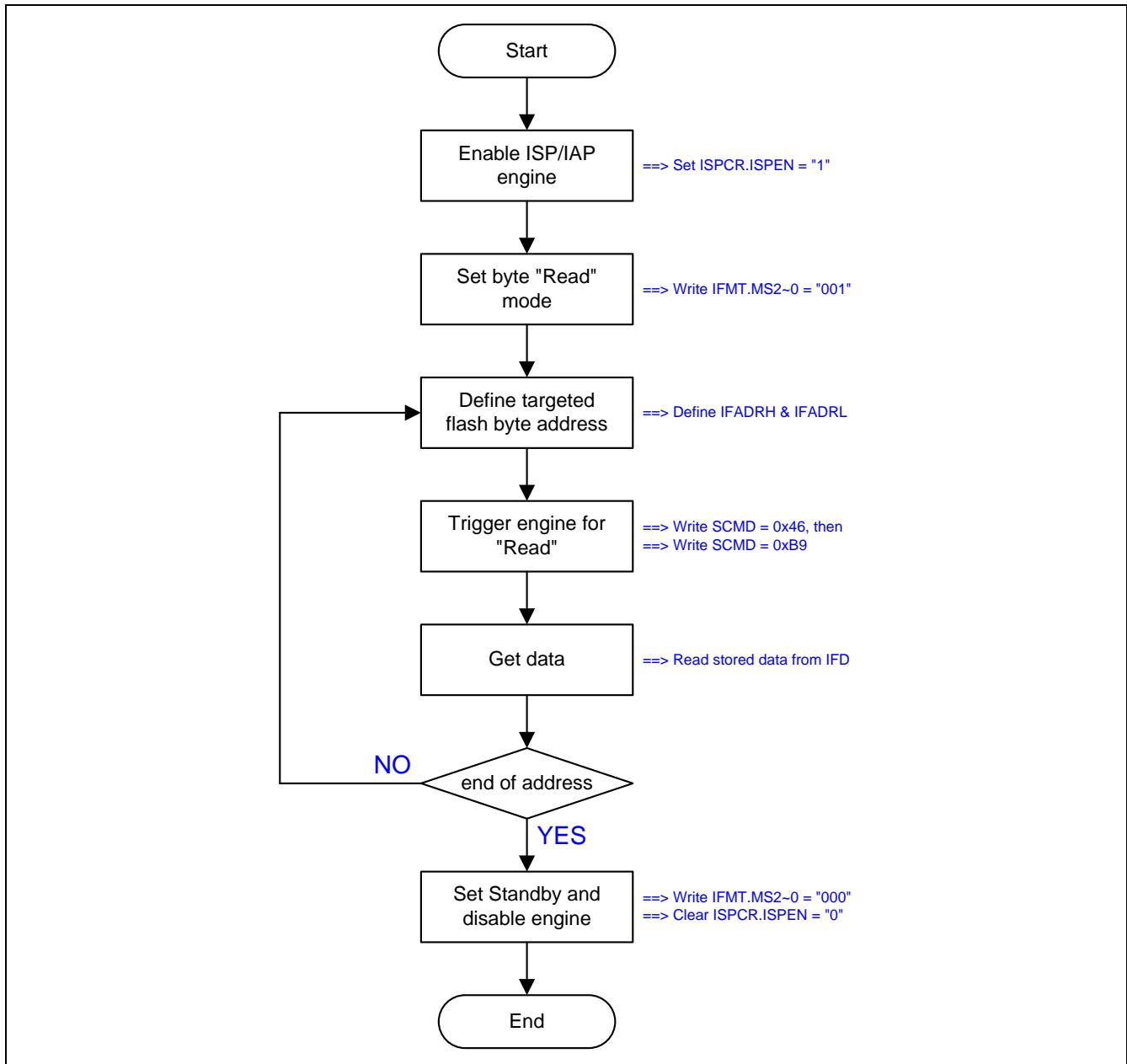

| 17.2.1. ISP/IAP Flash 编程模式 .....         | 112        |

| 17.2.2. ISP/IAP Flash 读模式 .....          | 114        |

| 17.3. ISP 操作 .....                       | 116        |

| 17.3.1. ISP 硬件途径 .....                   | 116        |

| 17.3.2. ISP 软件途径 .....                   | 116        |

| 17.3.3. ISP 注意事项 .....                   | 117        |

| 17.4. 在应用中编程 (IAP) .....                 | 118        |

| 17.4.1. IAP-存储边界/范围 .....                | 118        |

| 17.4.2. 更新 ISP 存储的数据 .....               | 118        |

| 17.4.3. IAP 注意事项 .....                   | 119        |

| 17.5. ISP/IAP 寄存器 .....                  | 120        |

| 17.6. ISP/IAP 示例代码 .....                 | 123        |

| <b>18. P 页特殊功能寄存器访问 .....</b>            | <b>131</b> |

| 18.1. P 页示例代码 .....                      | 134        |

| <b>19. 辅助特殊功能寄存器.....</b>                | <b>138</b> |

| <b>20. 硬件选项 .....</b>                    | <b>140</b> |

| <b>21. 应用说明 .....</b>                    | <b>142</b> |

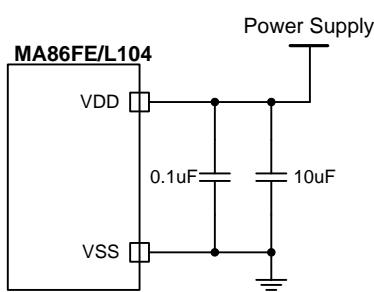

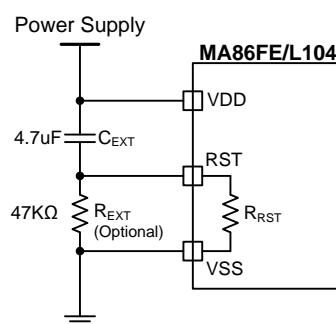

| 21.1. 电源电路 .....                         | 142        |

| 21.2. 复位电路 .....                         | 142        |

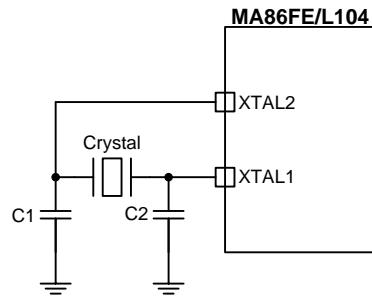

| 21.3. XTAL 振荡电路 .....                    | 143        |

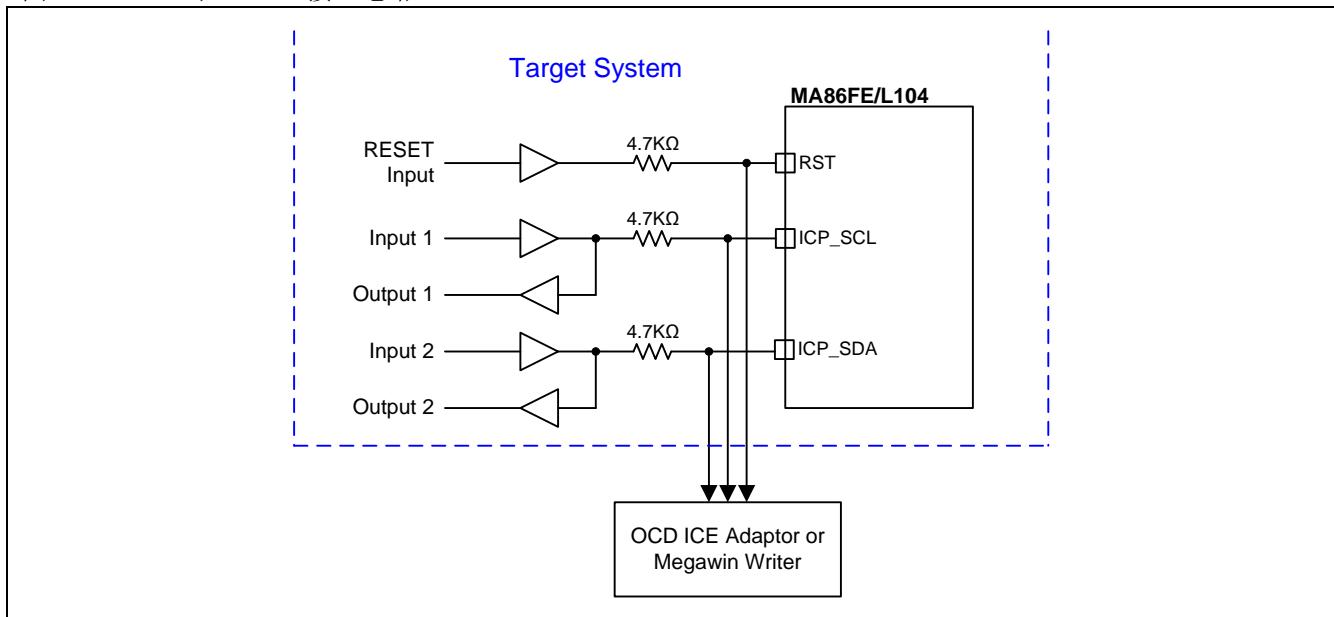

| 21.4. ICP 接口电路 .....                     | 144        |

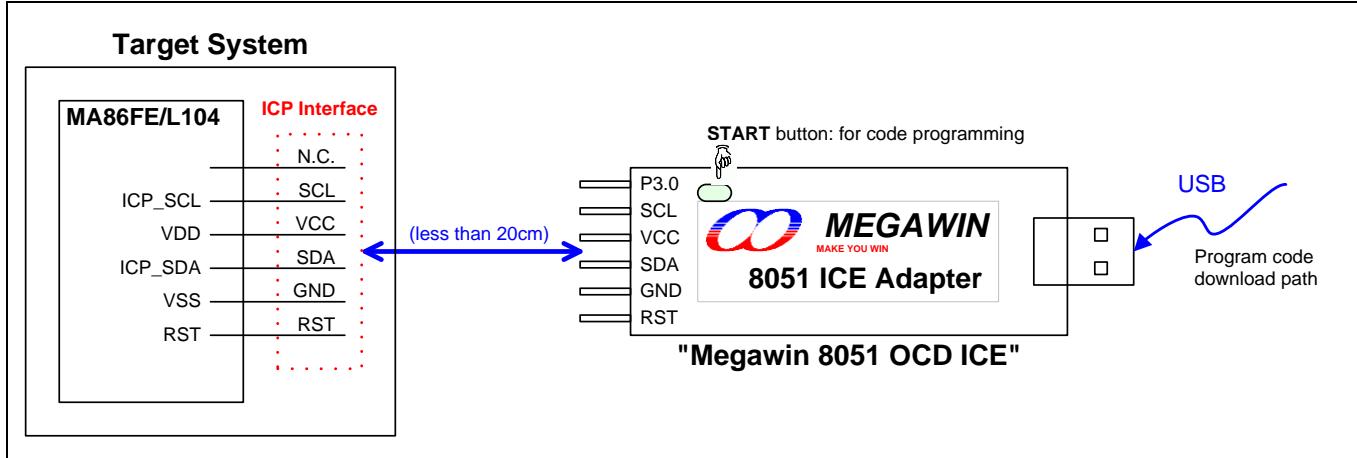

| 21.5. 在芯片编程功能 .....                      | 145        |

|                      |     |

|----------------------|-----|

| 22. 电气特性 .....       | 146 |

| 22.1. 最大绝对额定值 .....  | 146 |

| 22.2. 直流特性 .....     | 147 |

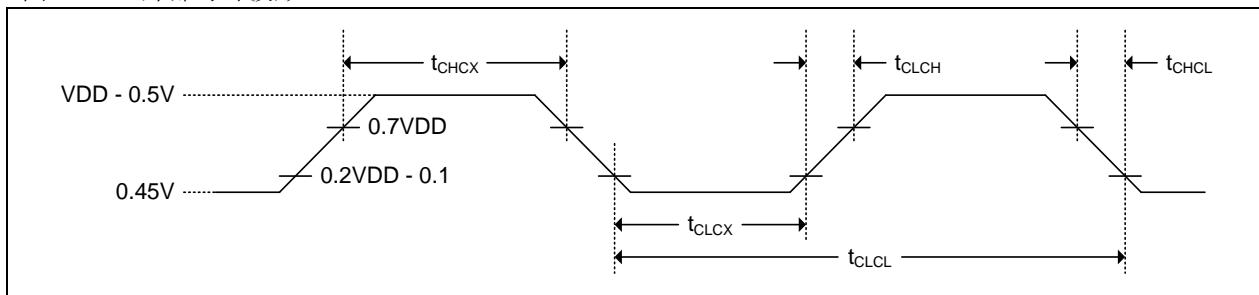

| 22.3. 外部时钟特性 .....   | 151 |

| 22.4. IHRCO 特性 ..... | 152 |

| 22.5. ILRCO 特性 ..... | 152 |

| 22.6. Flash 特性 ..... | 153 |

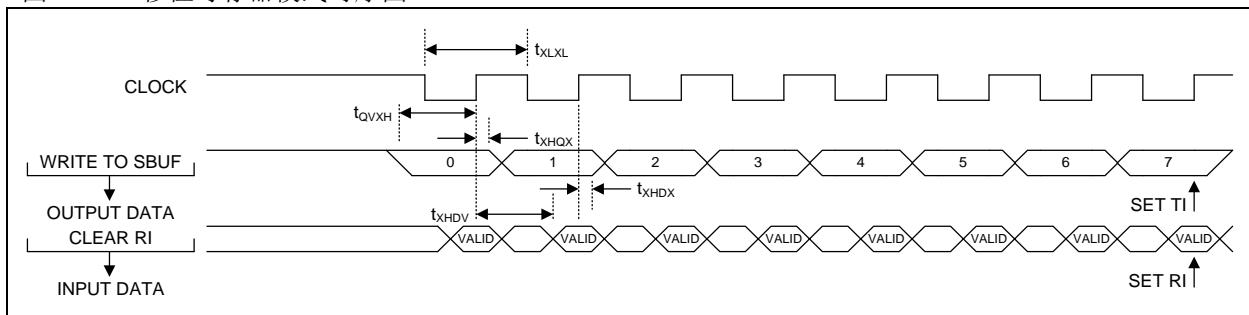

| 22.7. 串行口时序特性 .....  | 153 |

| 23. 指令集 .....        | 154 |

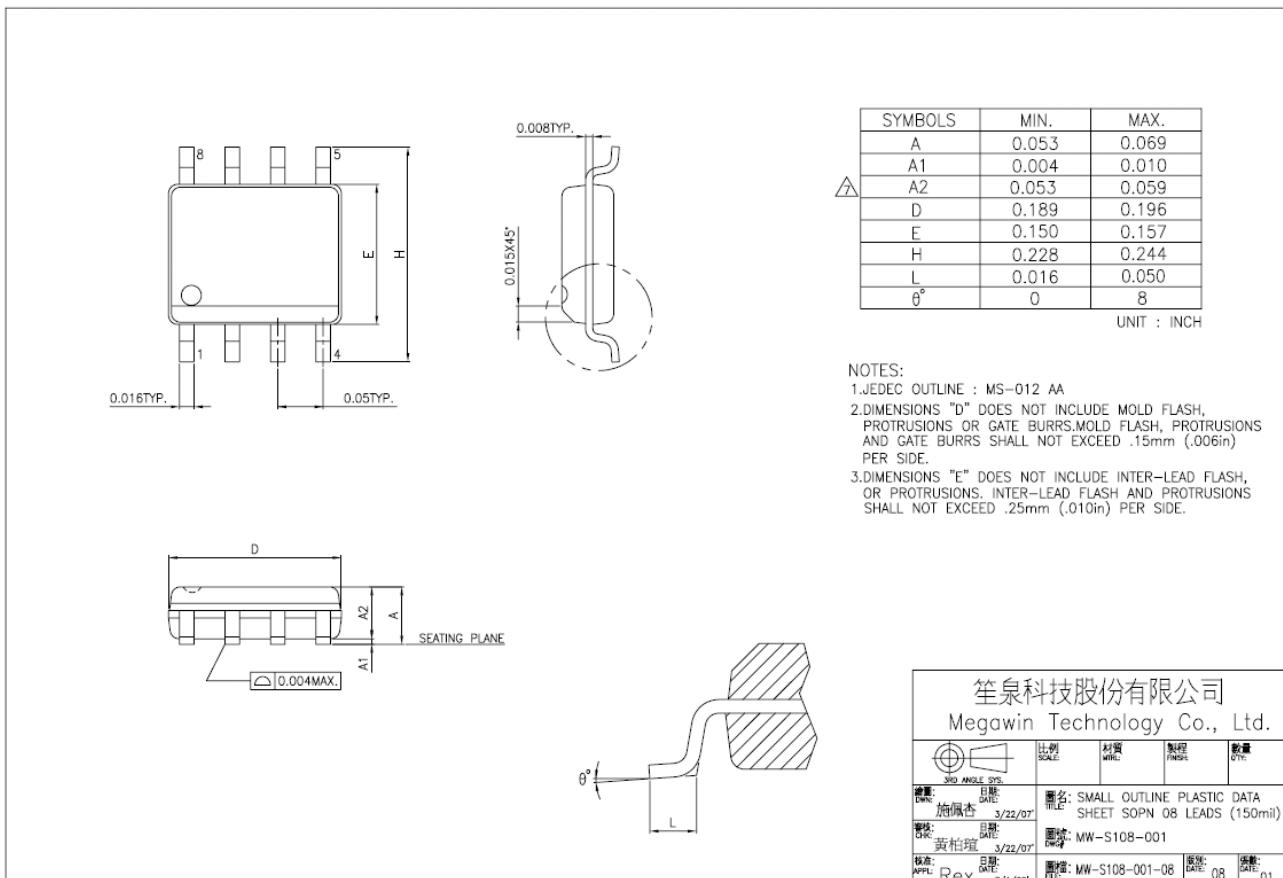

| 24. 封装尺寸 .....       | 159 |

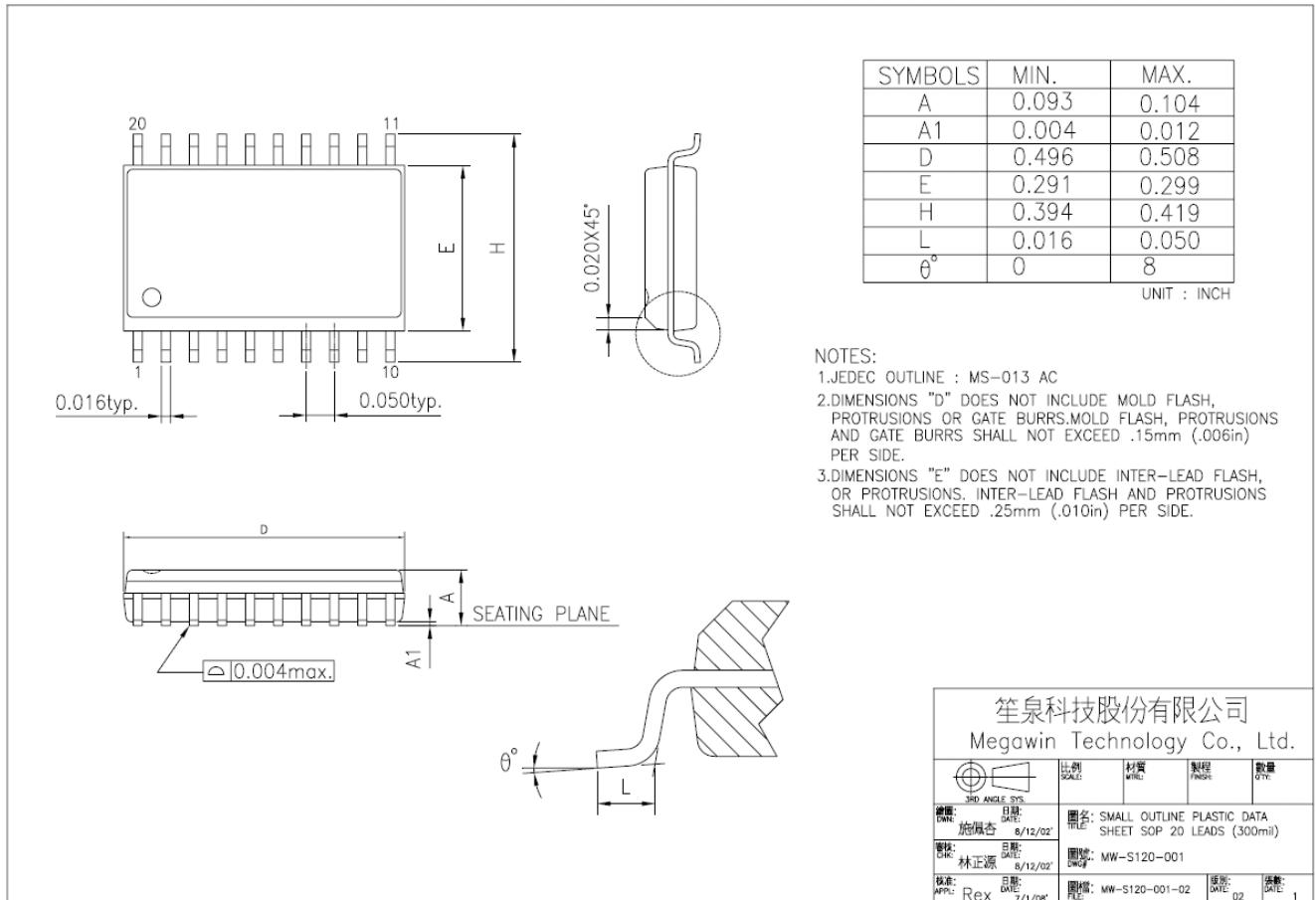

| 24.1. SOP-20 .....   | 159 |

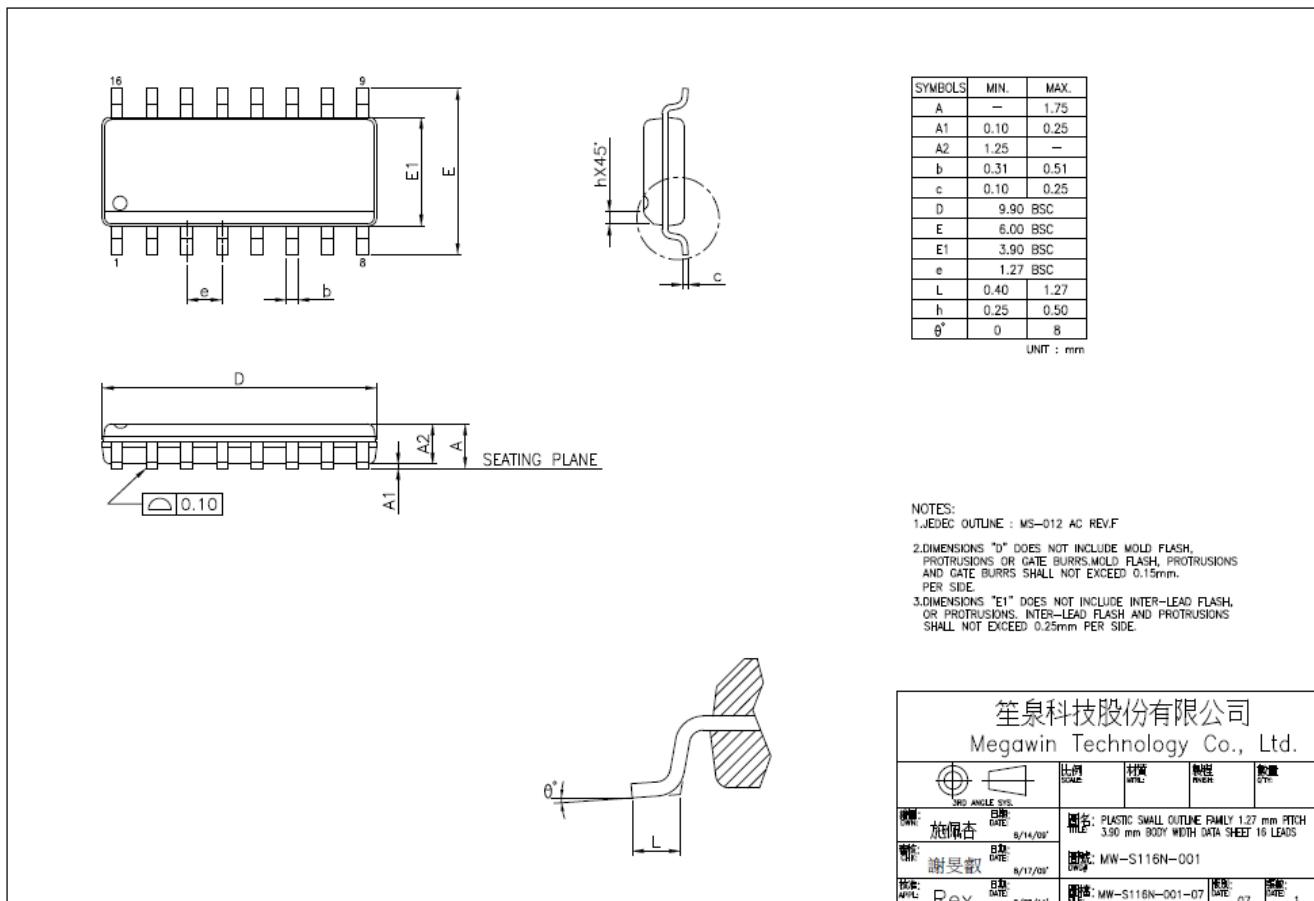

| 24.2. SOP-16 .....   | 160 |

| 24.3. SOP-8 .....    | 161 |

| 25. 修订历史 .....       | 162 |

## 1. 概述

**MA86E/L104**是基于80C51的高效1-T结构的单芯片微处理器，每条指令需要1~6 时钟信号（比标准的8051快 6~7 倍），与标准8051指令集兼容。因此在与标准8051有同样的处理能力的情况下，**MA86E/L104**只需要非常低的运行速度，同时由此能很大程度的减少耗电量。

**MA86E/L104**有 4K 字节的内置Flash存储器用于保存代码和数据。Flash存储器可以通过串行模式编程 (ICP，在电路编程) 或者 ISP 模式 (在系统编程) 进行编程的能力。同时，也提供在应用编程(IAP)的能力。ISP和ICP让使用者无需从产品中取下微控制器就可以下载新的代码；IAP意味着应用程序正在运行时，微控制器能够在Flash中写入不易失数据。这些功能都由内建的电荷泵提供编程用的高压。

**MA86E/L104**除了80C52 MCU的标准功能（例如 256 字节的随机存储器，二个8位I/O口，二个带有高/低触发选项的外部中断，一个多源4级中断控制和二个16位定时/计数器）外，**MA86E/L104** 有二个额外的 I/O 口 (P4.0 和 P4.1)，键盘中断，一次性使能的看门狗定时器。一个低电压检测器，一个外部的晶振，一个外部的晶振（与 P4.0 和 P4.1 共用），一个高精度的内部振荡(IHRCO)，一个低速的内部 RC 振荡器(ILRCO) 和一个多功能的增强型的串口(EUART) 和一个低速增强设备 (X2/X4 模式)。

**MA86E/L104 有多种工作模式可以减少耗电量：**空闲，掉电模式，慢频模式，副频模式，watch 模式和 monitor 模式。在空闲模式下，CPU被冻结而外围模块和中断系统依然活动。在掉电模式下，随机存储器RAM和特殊功能寄存器SFR的值被保存，而其他所有功能被终止。最重要的是，在掉电模式下的微控制器可以被多种中断或复位唤醒。在慢频模式，使用者可以通过8位的系统时钟分频器减慢系统速度以减少耗电量。选择副频模式系统时钟来自内部低速振荡器CPU 用一个特别慢的速度在运行。watch 模式，在掉电模式或空闲模式下保持WDT正常运行来唤醒CPU。Monitor 模式，在掉电模式检测电压，当电压特别低的时候会复位。

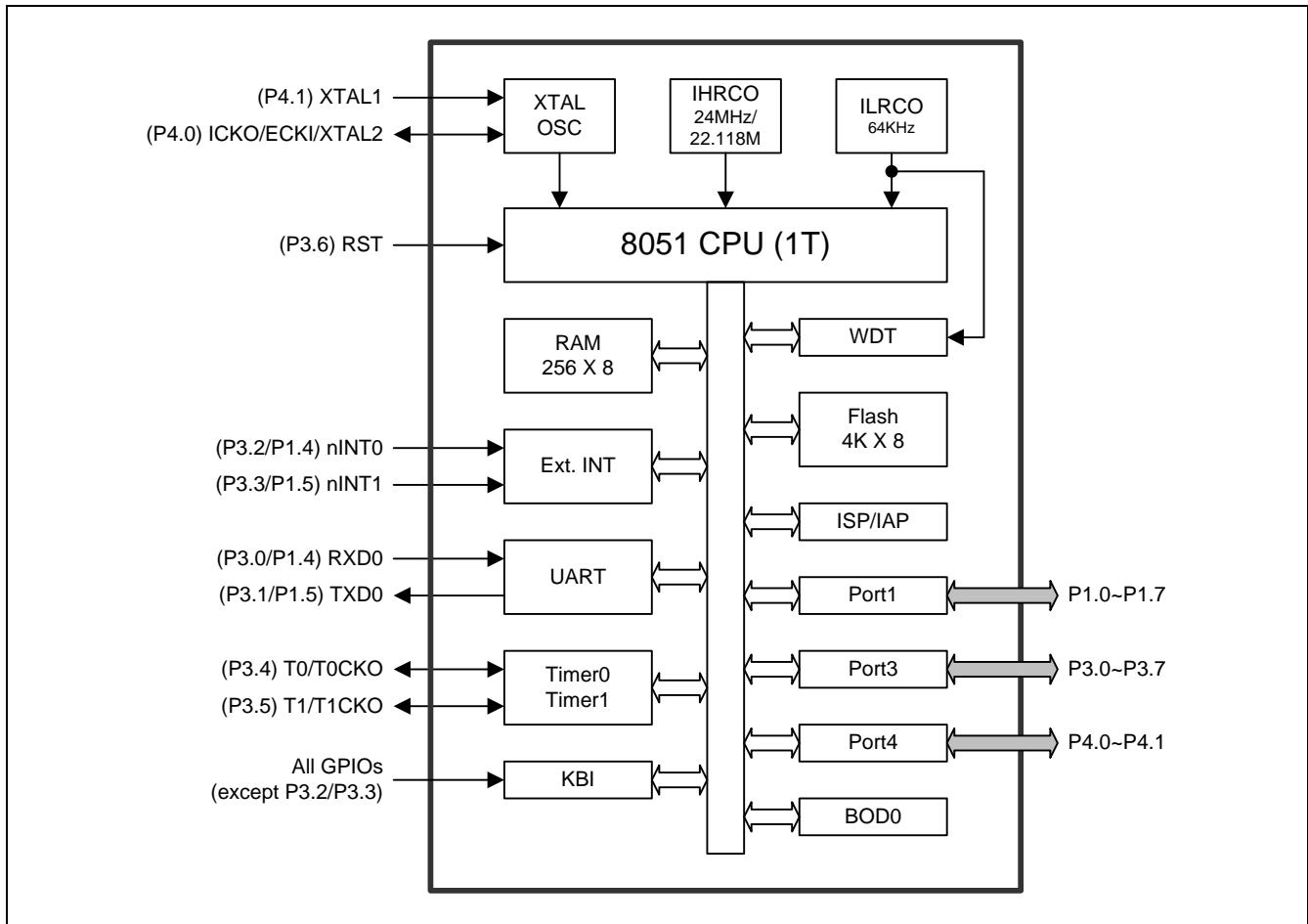

## 2. 方框图

图 2-1. 方框图

### 3. 特殊功能寄存器

#### 3.1. SFR 图

表 3-1. SFR 图

|           | 0/8        | 1/9        | 2/A        | 3/B        | 4/C        | 5/D        | 6/E        | 7/F        |

|-----------|------------|------------|------------|------------|------------|------------|------------|------------|

| <b>F8</b> | --         | --         | --         | --         | --         | --         | --         | --         |

| <b>F0</b> | B          | --         | --         | --         | --         | --         | --         | --         |

| <b>E8</b> | P4         | --         | --         | --         | --         | --         | --         | --         |

| <b>E0</b> | ACC        | WDTCR      | IFD        | IFADRH     | IFADRL     | IFMT       | SCMD       | ISPCR      |

| <b>D8</b> | --         | --         | --         | --         | --         | --         | --         | --         |

| <b>D0</b> | PSW        | --         | --         | --         | --         | --         | P3KBIE     | P1KBIE     |

| <b>C8</b> | --         | --         | --         | --         | --         | --         | --         | --         |

| <b>C0</b> | --         | --         | --         | --         | --         | --         | --         | CKCON0     |

| <b>B8</b> | IPOL       | SADEN      | --         | --         | --         | --         | --         | --         |

| <b>B0</b> | P3         | P3M0       | P3M1       | P4M0       | PUCON0     | --         | --         | IP0H       |

| <b>A8</b> | IE         | SADDR      | --         | --         |            | EIE1       | EIP1L      | EIP1H      |

| <b>A0</b> | --         | AUXR0      | AUXR1      | AUXR2      | --         | --         | --         | --         |

| <b>98</b> | SCON       | SBUF       | --         | --         | --         | --         | --         | --         |

| <b>90</b> | P1         | P1M0       | --         | --         | --         | --         | --         | PCON1      |

| <b>88</b> | TCON       | TMOD       | TL0        | TL1        | TH0        | TH1        | SFIE       | --         |

| <b>80</b> | --         | SP         | DPL        | DPH        | --         | --         | --         | PCON0      |

|           | <b>0/8</b> | <b>1/9</b> | <b>2/A</b> | <b>3/B</b> | <b>4/C</b> | <b>5/D</b> | <b>6/E</b> | <b>7/F</b> |

### 3.2. SFR 位分配

表 3-2. SFR 位分配

| 标号     | 描述                               | 地址  | 位地址和标号 |        |        |        |        |        |        |        | 复位值       |

|--------|----------------------------------|-----|--------|--------|--------|--------|--------|--------|--------|--------|-----------|

|        |                                  |     | Bit-7  | Bit-6  | Bit-5  | Bit-4  | Bit-3  | Bit-2  | Bit-1  | Bit-0  |           |

| SP     | Stack Pointer                    | 81H |        |        |        |        |        |        |        |        | 00000111B |

| DPL    | Data Pointer Low                 | 82H |        |        |        |        |        |        |        |        | 00000000B |

| DPH    | Data Pointer High                | 83H |        |        |        |        |        |        |        |        | 00000000B |

| PCON0  | Power Control 0                  | 87H | SMOD1  | SMOD0  | GF     | POF    | GF1    | GF0    | PD     | IDL    | 00010000B |

| TCON   | Timer Control                    | 88H | TF1    | TR1    | TF0    | TR0    | IE1    | IT1    | IE0    | IT0    | 00000000B |

| TMOD   | Timer Mode                       | 89H | GATE   | C/T    | M1     | M0     | GATE   | C/T    | M1     | M0     | 00000000B |

| TL0    | Timer Low 0                      | 8AH |        |        |        |        |        |        |        |        | 00000000B |

| TL1    | Timer Low 1                      | 8BH |        |        |        |        |        |        |        |        | 00000000B |

| TH0    | Timer High 0                     | 8CH |        |        |        |        |        |        |        |        | 00000000B |

| TH1    | Timer High 1                     | 8DH |        |        |        |        |        |        |        |        | 00000000B |

| SFIE   | System Flag INT En.              | 8EH | UTIE   | --     | --     | --     | KBIFIE | --     | BOF0IE | WDTFIE | 0xxx0x00B |

| P1     | Port 1                           | 90H | P1.7   | P1.6   | P1.5   | P1.4   | P1.3   | P1.2   | P1.1   | P1.0   | 11111111B |

| P1M0   | P1 Mode Register 0               | 91H | P1M0.7 | P1M0.6 | P1M0.5 | P1M0.4 | P1M0.3 | P1M0.2 | P1M0.1 | P1M0.0 | 00000000B |

| PCON1  | Power Control 1                  | 97H | SWRF   | EXRF   | --     | --     | KBIF   | --     | BOF0   | WDTF   | 00xx0x00B |

| SCON   | Serial Control                   | 98H | SM0/FE | SM1    | SM2    | REN    | TB8    | RB8    | Ti     | RI     | 00000000B |

| SBUF   | Serial Buffer                    | 99H |        |        |        |        |        |        |        |        | xxxxxxxB  |

| AUXR0  | Auxiliary Register 0             | A1H | P40OC1 | P40OC0 | P40FD  | GF     | P1FS1  | P1FS0  | INT1H  | INT0H  | 00000000B |

| AUXR1  | Auxiliary Register 1             | A2H | RTX3E  | RTX2E  | RTX1E  | RTX0E  | GF     | GF     | RXCS1  | RXCS0  | 00000000B |

| AUXR2  | Auxiliary Register 2             | A3H | URXR   | BTI    | URM0X6 | SMOD2  | T1X12  | T0X12  | T1CKOE | T0CKOE | 00000000B |

| IE     | Interrupt Enable                 | A8H | EA     | --     | --     | ES     | ET1    | EX1    | ET0    | EX0    | 00000000B |

| SADDR  | Slave Address                    | A9H |        |        |        |        |        |        |        |        | 00000000B |

| EIE1   | Extended INT Enable 1            | ADH | --     | --     | --     | --     | ESF    | --     | --     | --     | xxxx0xxxB |

| EIP1L  | Ext. INT Priority 1 Low          | AEH | --     | --     | --     | --     | PSFL   | --     | --     | --     | xxxx0xxxB |

| EIP1H  | Ext. INT Priority 1 High         | AFH | --     | --     | --     | --     | PSFH   | --     | --     | --     | xxxx0xxxB |

| P3     | Port 3                           | B0H | P3.7   | P3.6   | P3.5   | P3.4   | P3.3   | P3.2   | P3.1   | P3.0   | 11111111B |

| P3M0   | P3 Mode Register 0               | B1H | P3M0.7 | P3M0.6 | P3M0.5 | P3M0.4 | P3M0.3 | P3M0.2 | P3M0.1 | P3M0.0 | 00000000B |

| P3M1   | P3 Mode Register 1               | B2H | P3M1.7 | P3M1.6 | P3M1.5 | P3M1.4 | P3M1.3 | P3M1.2 | P3M1.1 | P3M1.0 | 00000000B |

| P4M0   | P4 Mode Register 0               | B3H | --     | --     | --     | --     | --     | --     | P4M0.1 | P4M0.0 | xxxxxx00B |

| PUCON0 | Pull-Up Control 0                | 92H | --     | PU40   | --     | --     | PU11   | PU10   | --     | --     | x0xx00xB  |

| IP0H   | Interrupt Priority 0 High        | B7H | --     | --     | --     | PSH    | PT1H   | PX1H   | PT0H   | PX0H   | 00000000B |

| IPOL   | Interrupt Priority Low           | B8H | --     | --     | --     | PSL    | PT1L   | PX1L   | PT0L   | PX0L   | 00000000B |

| SADEN  | Slave Address Mask               | B9H |        |        |        |        |        |        |        |        | 00000000B |

| CKCON0 | Clock Control 0                  | C7H | AFS    | --     | --     | --     | --     | SCKS2  | SCKS1  | SCKS0  | 0xxx000B  |

| PSW    | Program Status Word              | D0H | CY     | AC     | F0     | RS1    | RS0    | OV     | F1     | P      | 00000000B |

| P3KBI  | P3 KBI Enable                    | D6H | P37KBI | P36KBI | P35KBI | P34KBI | P41KBI | P40KBI | P31KBI | P30KBI | 00000000B |

| P1KBI  | P1 KBI Enable                    | D7H | P17KBI | P16KBI | P15KBI | P14KBI | P13KBI | P12KBI | P11KBI | P10KBI | 00000000B |

| ACC    | Accumulator                      | E0H | ACC.7  | ACC.6  | ACC.5  | ACC.4  | ACC.3  | ACC.2  | ACC.1  | ACC.0  | 00000000B |

| WDTCR  | Watch-dog-timer Control register | E1H | WREN   | NSW    | ENW    | CLW    | WIDL   | PS2    | PS1    | PS0    | 0x000000B |

| IFD    | ISP Flash data                   | E2H |        |        |        |        |        |        |        |        | 1111111B  |

| IFADRH | ISP Flash address High           | E3H |        |        |        |        |        |        |        |        | 00000000B |

| IFADRL | ISP Flash Address Low            | E4H |        |        |        |        |        |        |        |        | 00000000B |

| IFMT   | ISP Mode Table                   | E5H | --     | --     | --     | --     | --     | MS2    | MS1    | MS0    | xxxxx00B  |

| SCMD   | ISP Serial Command               | E6H |        |        |        |        |        |        |        |        | xxxxxxxxB |

| ISPCR  | ISP Control Register             | E7H | ISPEN  | BS     | SRST   | CFAIL  | --     | --     | --     | --     | 0000xxxxB |

| P4     | Port 4                           | E8H | --     | --     | --     | --     | --     | --     | P4.1   | P4.0   | xxxxx11B  |

| B      | B Register                       | F0H | B.7    | B.6    | B.5    | B.4    | B.3    | B.2    | B.1    | B.0    | 00000000B |

### 3.3. 辅助 SFR 图 (Page P)

**MA86E/L104 特殊功能寄存器 (SFR)** 有一个辅助索引 P 页，它写的方法跟标准的 8051 特殊功能寄存器的不一样。象访问 ISP/IAP 一样通过设置 IFMT 和 SCMD 来访问这个辅助的特殊功能寄存器。P 页有 256 字节有用到的为 5 个物理字节地址和 4 个逻辑字节地址。5 个物理字节地址包括 IAPLB, CKCON2, PCON2, SPCON0 和 DCON0。4 个逻辑字节地址包括 PCON0, PCON1, CKCON0 和 WDTCR。在 0~F 写这 4 个逻辑地址会得到相同的特殊功能 (SFR) 值。更多的细节请参考 P 页访问章节。

表 3-3. 辅助 SFR 图 (Page P)

|    | 0/8    | 1/9   | 2/A | 3/B   | 4/C   | 5/D | 6/E | 7/F    |

|----|--------|-------|-----|-------|-------|-----|-----|--------|

| F8 | --     | --    | --  | --    | --    | --  | --  | --     |

| F0 | --     | --    | --  | --    | --    | --  | --  | --     |

| E8 | --     | --    | --  | --    | --    | --  | --  | --     |

| E0 | --     | WDTCR | --  | --    | --    | --  | --  | --     |

| D8 | --     | --    | --  | --    | --    | --  | --  | --     |

| D0 | --     | --    | --  | --    | --    | --  | --  | --     |

| C8 | --     | --    | --  | --    | --    | --  | --  | --     |

| C0 | --     | --    | --  | --    | --    | --  | --  | CKCON0 |

| B8 | --     | --    | --  | --    | --    | --  | --  | --     |

| B0 | --     | --    | --  | --    | --    | --  | --  | --     |

| A8 | --     | --    | --  | --    | --    | --  | --  | --     |

| A0 | --     | --    | --  | --    | --    | --  | --  | --     |

| 98 | --     | --    | --  | --    | --    | --  | --  | --     |

| 90 | --     | --    | --  | --    | --    | --  | --  | PCON1  |

| 88 | --     | --    | --  | --    | --    | --  | --  | --     |

| 80 | --     | --    | --  | --    | --    | --  | --  | PCON0  |

| 78 | --     | --    | --  | --    | --    | --  | --  | --     |

| 70 | --     | --    | --  | --    | --    | --  | --  | --     |

| 68 | --     | --    | --  | --    | --    | --  | --  | --     |

| 60 | --     | --    | --  | --    | --    | --  | --  | --     |

| 58 | --     | --    | --  | --    | --    | --  | --  | --     |

| 50 | --     | --    | --  | --    | --    | --  | --  | --     |

| 48 | SPCON0 | --    | --  | --    | DCON0 | --  | --  | --     |

| 40 | CKCON2 | --    | --  | --    | PCON2 | --  | --  | --     |

| 38 | --     | --    | --  | --    | --    | --  | --  | --     |

| 30 | --     | --    | --  | --    | --    | --  | --  | --     |

| 28 | --     | --    | --  | --    | --    | --  | --  | --     |

| 20 | --     | --    | --  | --    | --    | --  | --  | --     |

| 18 | --     | --    | --  | --    | --    | --  | --  | --     |

| 10 | --     | --    | --  | --    | --    | --  | --  | --     |

| 08 | --     | --    | --  | --    | --    | --  | --  | --     |

| 00 | --     | --    | --  | IAPLB | --    | --  | --  | --     |

|    | 0/8    | 1/9   | 2/A | 3/B   | 4/C   | 5/D | 6/E | 7/F    |

### 3.4. 辅助 SFR 位分配 (Page P)

表 3-4. 辅助 SFR 位分配 (Page P)

| S 标号                  | 描述                               | 地址  | 位地址和标号 |        |        |        |        |        |        |        | 复位值                    |

|-----------------------|----------------------------------|-----|--------|--------|--------|--------|--------|--------|--------|--------|------------------------|

|                       |                                  |     | Bit-7  | Bit-6  | Bit-5  | Bit-4  | Bit-3  | Bit-2  | Bit-1  | Bit-0  |                        |

| <b>Physical Bytes</b> |                                  |     |        |        |        |        |        |        |        |        |                        |

| IAPLB                 | IAP Low Boundary                 | 03H | IAPLB6 | IAPLB5 | IAPLB4 | IAPLB3 | IAPLB2 | IAPLB1 | IAPLB0 | --     | 00001000B              |

| CKCON2                | Clock Control 2                  | 40H | 0      | 0      | XTALE  | IHRCOE | 0      | 0      | OSCS1  | OSCS0  | 00010000B              |

| PCON2                 | Power Control 2                  | 44H | 0      | AWBODO | 0      | 0      | 0      | 0      | BO0RE  | 1      | 00000001B              |

| SPCON0                | SFR Page Control 0               | 48H | 0      | 0      | 0      | WRCTL  | 0      | CKCTL0 | PWCTL1 | PWCTL0 | 00000000B              |

| DCON0                 | Device Control 0                 | 4CH | HSE    | IAPO   | 0      | 0      | 0      | 0      | RSTIO  | 0      | 10000010B              |

| <b>Logical Bytes</b>  |                                  |     |        |        |        |        |        |        |        |        |                        |

| PCON0                 | Power Control 0                  | 87H | SMOD1  | SMOD0  | GF     | POF    | GF1    | GF0    | PD     | IDL    | 00010000B              |

| PCON1                 | Power Control 1                  | 97H | SWRF   | EXRF   | --     | --     | KBIF   | --     | BOF0   | WDTF   | 00xx0x00B              |

| CKCON0                | Clock Control 0                  | C7H | AFS    | --     | --     | --     | --     | SCKS2  | SCKS1  | SCKS0  | 0xxxx001B              |

| WDTCR                 | Watch-dog-timer Control register | E1H | WREN   | NSW    | ENW    | CLW    | WIDL   | PS2    | PS1    | PS0    | 00000000B<br>xxx0xxxxB |

写入 P 页 SFR 例程:

```

IFADRH = 0x00;

ISPCR = ISPEN;                                //使能 IAP/ISP 功能

IFMT = MS2;                                     // P 页写, IFMT =0x04

IFADRL = SPCON0;                               //相对应的 P 页 SFR 设置 P 页 SFR 地址

IFD |= CKCTL0;                                 // 设置 CKCTL0

SCMD = 0x46;                                    //

SCMD = 0xB9;                                    //

IFMT = Flash_Standby;                          // IAP/ISP 备用模式, IFMT =0x00

ISPCR &= ~ISPEN;

```

## 4. 引脚结构

### 4.1. 封装指南

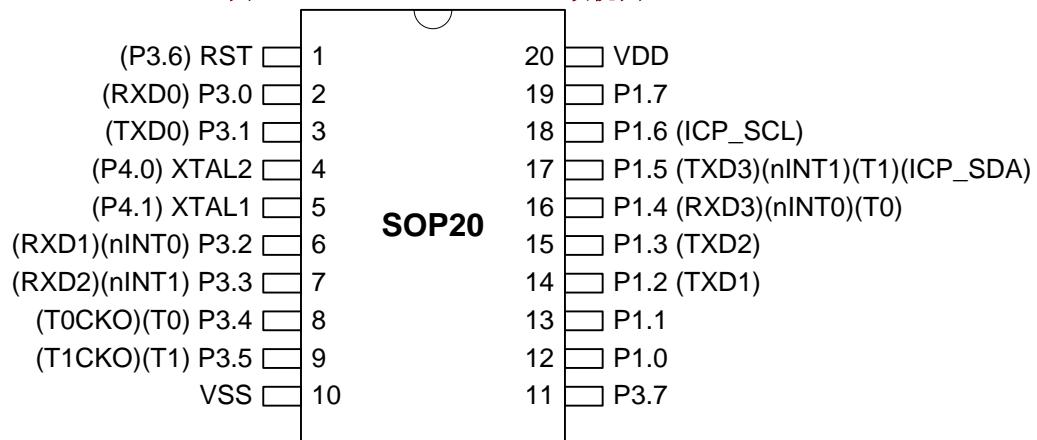

图 4-1. MA86E/L104AS20 顶视图

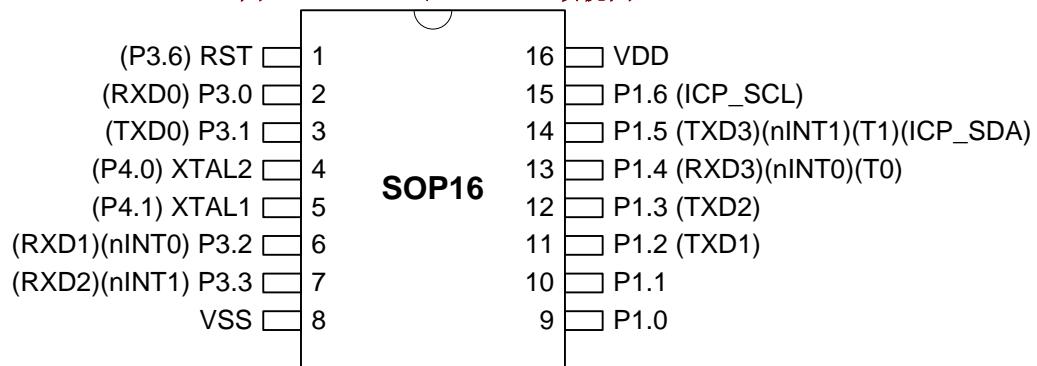

图 4-2. MA86E/L104AS16 顶视图

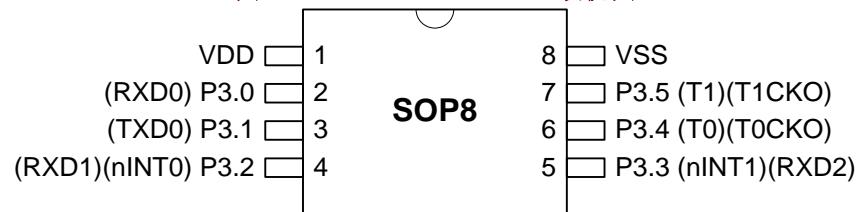

图 4-3. MA86E/L104AS8 顶视图

## 4.2. 引脚定义

表 4-1. 引脚定义

| 助记符                                            | 引脚号           |               |              | I/O<br>类型          | 描述                                                                                                                                                                                                  |

|------------------------------------------------|---------------|---------------|--------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                | 20-Pin<br>SOP | 16-Pin<br>SOP | 8-Pin<br>SOP |                    |                                                                                                                                                                                                     |

| P1.0                                           | 12            | 9             | --           | I/O                | * Port 1.0.                                                                                                                                                                                         |

| P1.1                                           | 13            | 10            | --           | I/O                | * Port 1.1.                                                                                                                                                                                         |

| P1.2<br>(TXD1)                                 | 14            | 11            | --           | I/O                | * Port 1.2.<br>* TXD1: TXD channel 1 output of UART repeater.                                                                                                                                       |

| P1.3<br>(TXD2)                                 | 15            | 12            | --           | I/O                | * Port 1.3.<br>* TXD2: TXD channel 2 output of UART repeater.                                                                                                                                       |

| P1.4<br>(RXD3)<br>(nINT0)<br>(T0)              | 16            | 13            | --           | I/O                | * Port 1.4.<br>* RXD3: RXD channel 3 input of UART repeater.<br>* nINT0: Alternate function for nINT0 input.<br>* T0: Alternate function for T0 input.                                              |

| P1.5<br>(TXD3)<br>(nINT1)<br>(T1)<br>(ICP_SDA) | 17            | 14            | --           | I/O                | * Port 1.5.<br>* TXD3: TXD channel 3 output of UART repeater.<br>* nINT1: Alternate function for nINT1 input.<br>* T1: Alternate function for T1 input.<br>* ICP_SDA: Serial data of ICP interface. |

| P1.6<br>(ICP_SCL)                              | 18            | 15            | --           | I/O                | * Port 1.6.<br>* ICP_SCL: Serial clock of ICP interface.                                                                                                                                            |

| P1.7                                           | 19            | --            | --           | I/O                | * Port 1.7.                                                                                                                                                                                         |

| P3.0<br>(RXD0)                                 | 2             | 2             | 2            | I/O                | * Port 3.0.<br>* RXD0: UART0 serial input port.                                                                                                                                                     |

| P3.1<br>(TXD0)                                 | 3             | 3             | 3            | I/O                | * Port 3.1.<br>* TXD0: UART0 serial output port.                                                                                                                                                    |

| P3.2<br>(nINT0)<br>(RXD1)                      | 6             | 6             | 4            | I/O                | * Port 3.2.<br>* nINT0: external interrupt 0 input.<br>* RXD3: RXD channel 3 input of UART repeater.                                                                                                |

| P3.3<br>(nINT1)<br>(RXD2)                      | 7             | 7             | 5            | I/O                | * Port 3.3.<br>* nINT1: external interrupt 1 input.<br>* RXD3: RXD channel 3 input of UART repeater.                                                                                                |

| P3.4<br>(T0)<br>(T0CKO)                        | 8             | --            | 6            | I/O                | * Port 3.4.<br>* T0: Timer/Counter 0 external input.<br>* T0CKO: programmable clock-out from Timer 0.                                                                                               |

| P3.5<br>(T1)<br>(T1CKO)                        | 9             | --            | 7            | I/O                | * Port 3.5.<br>* T1: Timer/Counter 1 external input.<br>* T1CKO: programmable clock-out from Timer 1.                                                                                               |

| P3.7                                           | 11            | --            | --           | I/O                | * Port 3 bit-7.                                                                                                                                                                                     |

| P4.0<br>(XTAL2)<br>(ECKI)<br>(ICKO)            | 4             | 4             | --           | I/O<br>O<br>I<br>O | * Port 4.0.<br>* XTAL2: Output of on-chip crystal oscillating circuit.<br>* ECKI: In external clock input mode, this is clock input pin.<br>* ICKO: IHRCO clock output.                             |

| P4.1<br>(XTAL1)                                | 5             | 5             | --           | I/O<br>I           | * Port 4.1<br>* XTAL1: Input of on-chip crystal oscillating circuit.                                                                                                                                |

| RST<br>(P3.6)                                  | 1             | 1             | --           | I<br>I/O           | ** RST: External RESET input, high active.<br>* Port 3.6. RST has the alternate function for P3.6.                                                                                                  |

| VDD                                            | 20            | 16            | 1            | P                  | Power supply input.                                                                                                                                                                                 |

| VSS                                            | 10            | 8             | 8            | G                  | Ground, 0 V reference.                                                                                                                                                                              |

### 4.3. 备选功能转换

许多 I/O 口，除了有普通的 I/O 功能外，还得为内置的外设提供备选功能。默认状态下，端口 1 和端口 0 为外设 UART, Timer0, Timer1, nINT0 和 nINT1 提供备选功能。然而，用户可以通过设置相对应的控制位选择 P1.4 和 P1.5 提供备选功能。这是特别有用的软件编程。

#### AUXR0: 辅助寄存器 0

SFR 页 = Normal

SFR 地址 = 0xA1

复位值 = 000x-0000

| 7      | 6      | 5     | 4  | 3     | 2     | 1     | 0     |

|--------|--------|-------|----|-------|-------|-------|-------|

| P40OC1 | P40OC0 | P40FD | -- | P1FS1 | P1FS0 | INT1H | INT0H |

| R/W    | R/W    | R/W   | W  | R/W   | R/W   | R/W   | R/W   |

Bit 7~6: P4.0 功能配置控制位 1 和 0。这两位仅在系统时钟来源选择为 IHRCO 时有效。在 crystal 模式，P4.0 和 P4.1 的功能是 XTAL2 和 XTAL1。在外部时钟输入模式，P4.0 被定义为时钟输入引脚。在 IHRCO 工作时，P4.0 提供作为 GPIO 或时钟源发生器的选项。当 P40OC[1:0]索引到非 P4.0GPIO 功能时，P4.0 将驱动 IHRCO 输出为其它设备提供时钟源。

| P40OC[1:0] | P4.0 功能 | I/O 模式    |

|------------|---------|-----------|

| 00         | P40     | By P4M0.0 |

| 01         | IHRCO   | By P4M0.0 |

| 10         | IHRCO/2 | By P4M0.0 |

| 11         | IHRCO/4 | By P4M0.0 |

当 P4.0 作为时钟输出功能时，相对应的设置 P4M0.0 为 “1” 它能选择 P4.0 作为推挽输出模式

Bit 3~2: P1.4 和 P1.5 备选功能选项.

| P1FS[1:0] | P1.4            | P1.5            |

|-----------|-----------------|-----------------|

| 00        | P1.4            | P1.5            |

| 01        | --              | Output for TxD1 |

| 10        | Input for nINT0 | Input for nINT1 |

| 11        | Input for T0    | Input for T1    |

## 5. 8051 CPU 功能描述

### 5.1. CPU 寄存器

#### PSW: 程序状态字

SFR 地址 = 0xD0

复位值 = 0000-0000

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| CY  | AC  | F0  | RS1 | RS0 | OV  | F1  | P   |

| R/W |

CY: 进位标志

AC: 辅助进位标志

F0: 用户可设定的标志位 0

RS1: 寄存器组选择位 1

RS0: 寄存器组选择位 0

OV: 溢出标志

F1: 用户可设定的标志位 1

P: 奇偶标志

程序状态字 (PSW) 包含反映 CPU 当前状态的几个状态位。PSW 属于特殊功能寄存器 SFR 区，包含进位标志，辅助进位标志 (应用于 BCD 操作)，两个寄存器组选择位，溢出标志，奇偶标志和两个用户可设定的标志位。

进位标志，不仅有算术运算的进位功能，也充当许多布尔运算的“累加器”。

RS0 和 RS1 被用来选择 4 组中的任意一组寄存器组，详见内部 RAM 章节 7.2。

奇偶位反映 1S 内累加器数字和的状况，1S 内累加器中数字和是奇数则 P=1 否则 P=0。

#### SP: 堆栈指针

SFR 地址 = 0x81

复位值 = 0000-0111

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SP[7] | SP[6] | SP[5] | SP[4] | SP[3] | SP[2] | SP[1] | SP[0] |

| R/W   |

堆栈指针保持栈顶位置，每执行一个 PUSH 指令，会自动增加，缺损值为 0X07H。

#### DPL: 数据指针低字节

SFR 地址 = 0x82

复位值 = 0000-0000

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| DPL[7] | DPL[6] | DPL[5] | DPL[4] | DPL[3] | DPL[2] | DPL[1] | DPL[0] |

| R/W    |

DPL 是 DPTR 的低字节，DPTR 用来间接访问 XRAM 和程序空间。

#### DPH: 数据指针高字节

SFR 地址 = 0x83

RESET = 0000-0000

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| DPH[7] | DPH[6] | DPH[5] | DPH[4] | DPH[3] | DPH[2] | DPH[1] | DPH[0] |

| R/W    |

DPH 是 DPTR 的高字节，DPTR 用来间接访问 XRAM 和程序空间。

### **ACC: 累加器**

SFR 地址 = 0xE0

复位值 = 0000-0000

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ACC.7 | ACC.6 | ACC.5 | ACC.4 | ACC.3 | ACC.2 | ACC.1 | ACC.0 |

| R/W   |

算术运算的累加器。

### **B: B 寄存器**

SFR 地址 = 0xF0

复位值 = 0000-0000

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| B.7 | B.6 | B.5 | B.4 | B.3 | B.2 | B.1 | B.0 |

| R/W |

另一个算术运算的累加器

## 5.2. CPU 时序

**MA86E/L104**是基于80C51的高效1-T结构的单芯片微处理器，与8051指令集兼容，每条指令需要1~6个时钟信号(比标准8051快6~7倍)。使用流线型结构同标准的8051结构比较大大增加了指令完成的速度，指令的时序也和标准的8051不同。

多数8051执行指令，一个区别是建立在机器周期和时钟周期之间，机器周期来自2到12个时钟周期长度。然而，1-T结构的80C51执行指令是基于单独的时钟周期时序。所有指令时序被指定在时钟周期期间。关于1T-80C51指令更详细的说明，请参考“指令集”，这里有每一条指令的助记符、字节数、时钟周期数。

## 5.3. CPU 寻址 模式

### **直接寻址(DIR)**

直接寻址时操作数用指令中一个8位地址的区域表示，只有内部数据存储器和特殊功能寄存器可以直接寻址。

### **间接寻址(IND)**

间接寻址时指令用一个包含操作数地址的寄存器表示，内部和外部存储器均可间接寻址。

8位地址的地址寄存器可以是选中区的 R0 或 R1 或堆栈指针，16位地址的地址寄存器只能是16位的“数据指针”寄存器，DPTR。

### **寄存器操作（寻址）(REG)**

包含从 R0 到 R7 的寄存器区可以被某些指令存取，这些指令的操作码中用 3 位寄存器说明。存取寄存器的指令有更高的代码效率，因为这种模式减少了一个地址字节。当指令被执行时，其中被选取的区一个 8 位寄存器被存取。执行时，用 PSW 寄存器中两位区选择位来选择四分之一区。

### **特殊寄存器寻址（寄存器间接寻址）**

一些指令具有一个特定的寄存器，例如，一些指令常用于累加器，或数据指针等等，所以没有需要指向它的地址字节。操作码本身就行了。有关累加器的指令 A 就是累加器的特殊操作码。

### **立即寻址(IMM)**

常量的数值可以在程序存储器中跟随操作码。

## 索引寻址

索引寻址只能访问程序存储器，且只读。这种寻址模式用查表法读取程序存储器。一个16位基址寄存器（数据指针DPTR或程序计数器PC）指向表的基地址，累加器提供偏移量。程序存储器中表项目地址由基地址加上累加器数据后形成。另一种索引寻址方式是利用“case jump”指令。跳转指令中的目标地址是基地址加上累加器数据后的值。

## 6. 存储器组织

像所有的 80C51 一样，**MA86E/L104** 的程序存储器和数据存储器的地址空间是分开的，这样 8 位微处理器可以通过一个 8 位的地址快速而有效的访问数据存储器。

程序存储器(ROM)只能读取，不能写入。最大可以达到 4K 字节。在 **MA86E/L104** 中，所有的程序存储器都是片上 Flash 存储器。因为没有设计外部程序使能 (/EA) 和编程使能 (/PSEN) 信号，所以不允许外接程序存储器。

数据存储器使用与程序存储器不同的地址空间。**MA86E/L104** 只有 256 字节的内部没有任何外部的数据存储器。

### 6.1. 程序存储器

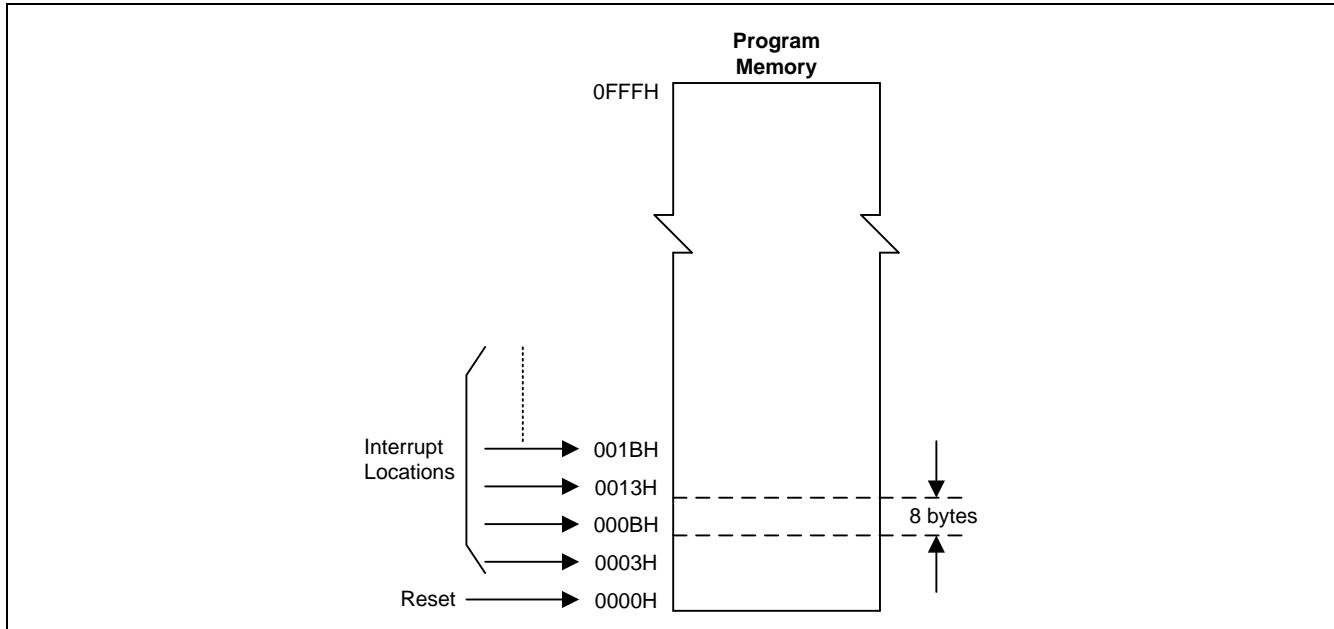

程序存储器用来保存让 CPU 进行处理的程序代码，如图 7-1 所示。复位后，CPU 从地址为 0000H 的地方开始运行，用户应用代码的起始部分应该放在这里。为了响应中断，中断服务位置(被称为中断矢量)应该位于程序存储器。每个中断在程序存储器中有一个固定的起始地址，中断使 CPU 跳到这个地址运行中断服务程序。举例来说，外部中断 0 被指定到地址 0003H，如果使用外部中断 0，那么它的中断服务程序一定是从 0003H 开始的。如果中断未被使用，那么这些地址就可以被一般的程序使用。

中断服务程序的起始地址之间有 8 字节的地址间隔：外部中断 0，0003H；定时器 0，000BH；外部中断 1，0013H；定时器 1，001BH 等等。如果中断服务程序足够短，它完全可以放在这 8 字节的空间中。如果其他的中断也被使用的话，较长的中断服务程序可以通过一条跳转指令越过后面的中断服务起始地址。

图 7-1 程序存储器

## 6.2. 数据存储器

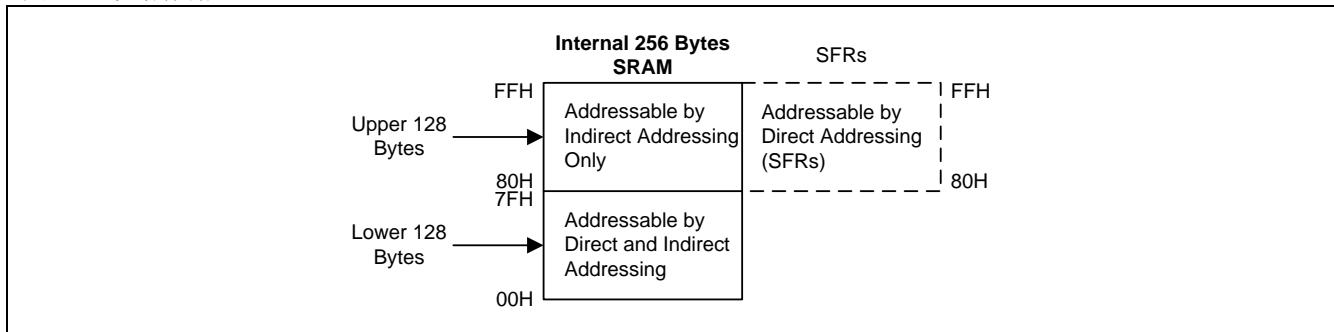

图 7-2 向 MA86E/L104 使用者展示了内部和外部数据存储器的空间划分。内部数据存储器被划分为三部分，通常被称为低 128 字节 RAM，高 128 字节 RAM 和 128 字节 SFR 空间。内部数据存储器的地址线只有 8 位宽，因此地址空间只有 256 字节。SFR 空间的地址高于 7FH，用直接地址访问；而用间接访问的方法访问高 128 字节的 RAM。这样虽然 SFR 和高 128 字节 RAM 占用相同的地址空间（80H—FFH），但他们实际上是分开的。

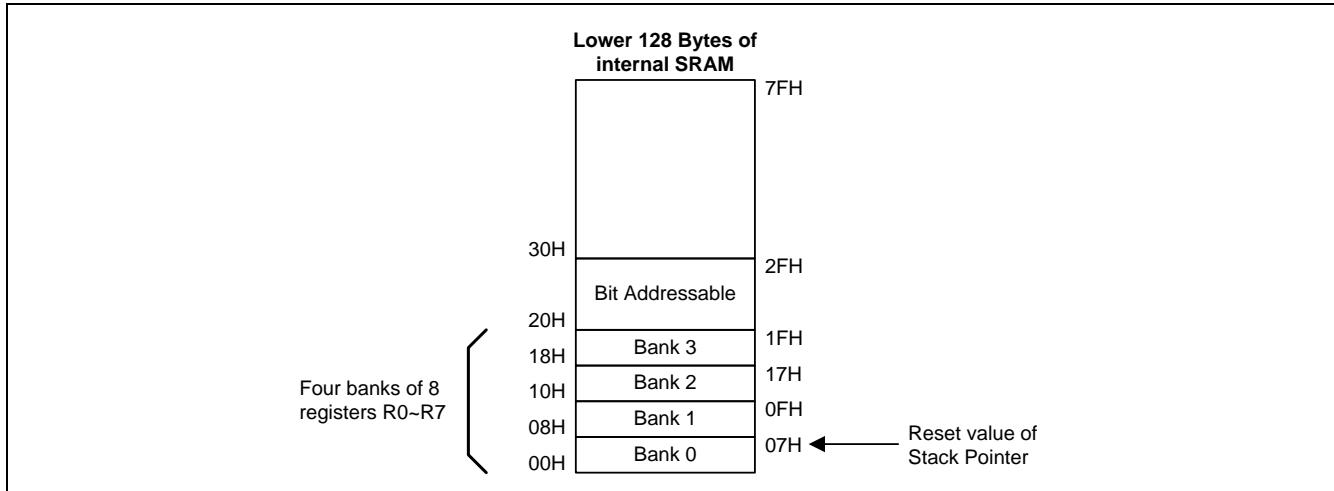

如图 7-3 所示，低 128 字节 RAM 与所有 80C51 一样。最低的 32 字节被划分为 4 组每组 8 字节的寄存器组。指令中称这些寄存器为 R0 到 R7。程序状态字 (PSW) 中的两位用于选择哪组寄存器被使用。这使得程序空间能够被更有效的使用，因为对寄存器访问的指令比使用直接地址的指令短。接下来的 16 字节是可以位寻址的存储器空间。80C51 的指令集包含一个位操作指令集，这区域中的 128 位可以被这些指令直接使用。位地址从 00H 开始到 7FH 结束。

所有的低 128 字节 RAM 都可以用直接或间接地址访问，而高 128 字节 RAM 只能用间接地址访问。

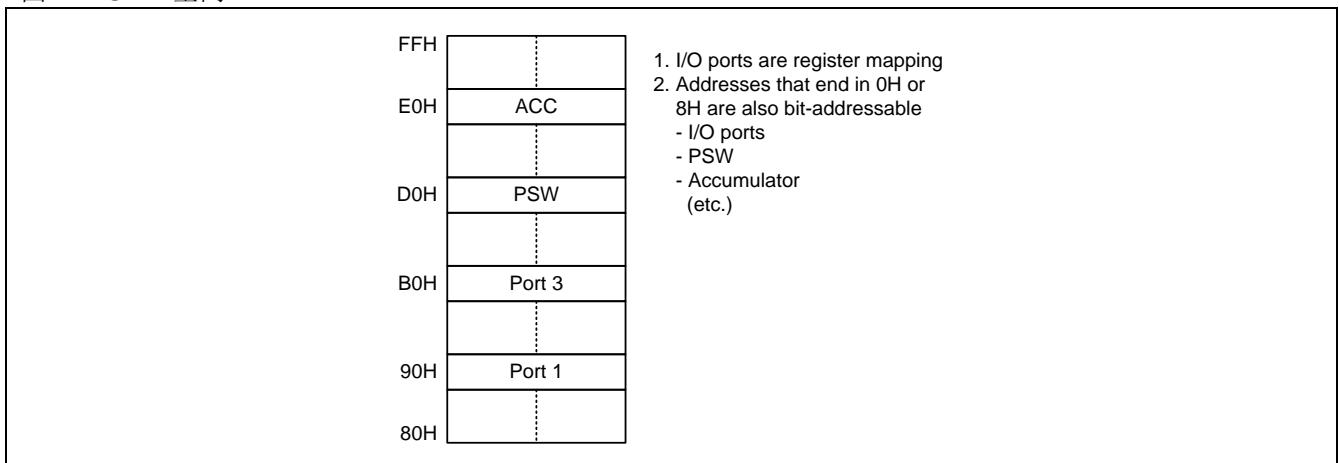

图 7-4 给出了特殊功能寄存器 (SFR) 的概览。SFR 包括端口寄存器，定时器和外围器件控制器，这些寄存器只能用直接地址访问。SFR 空间中有 16 个地址同时支持位寻址和直接寻址。可以位寻址的 SFR 的地址末位是 0H 或 8H。

图 7-2 数据存储器

图 7-3 内部 RAM 的低 128 字节

图 7-4 SFR 空间

### 6.3. 关于 C51 编译器的声明标识符

C51 编译器的声明识别符与 MA86E/L104 存储空间的对应关系如下：

#### ***data***

128 字节的内部数据存储空间 (00h~7Fh)。使用除 MOVX 和 MOVC 以外的指令，可以直接或间接的访问。全部或部分的堆栈可能保存在此区域中。

#### ***idata***

间接数据。256 字节的内部数据存储空间 (00h~FFh) 使用除 MOVX 和 MOVC 以外的指令间接访问。全部或部分的堆栈可能保存在此区域中。此区域包括 data 区 和 data 区以上的 128 字节。

#### ***sfr***

特殊功能寄存器。CPU 寄存器和外围部件控制/状态寄存器，只能通过直接地址访问。

#### ***xdata***

没有外部数据或片上的扩展 RAM (XRAM)。

#### ***pdata***

没有分页的外部数据(256 字节) 或片上的扩展 RAM (XRAM)。

#### ***code***

4K 程序存储空间。通过“MOVC @A+DTPR”访问，作为程序部分被读取。

## 7. 数据指针寄存器 (DPTR)

MA86E/L104 DPTR 只有一种设置。 MA86E/L104 不支持访问外部存储器和 MOVX 指令。

## 8. 系统时钟

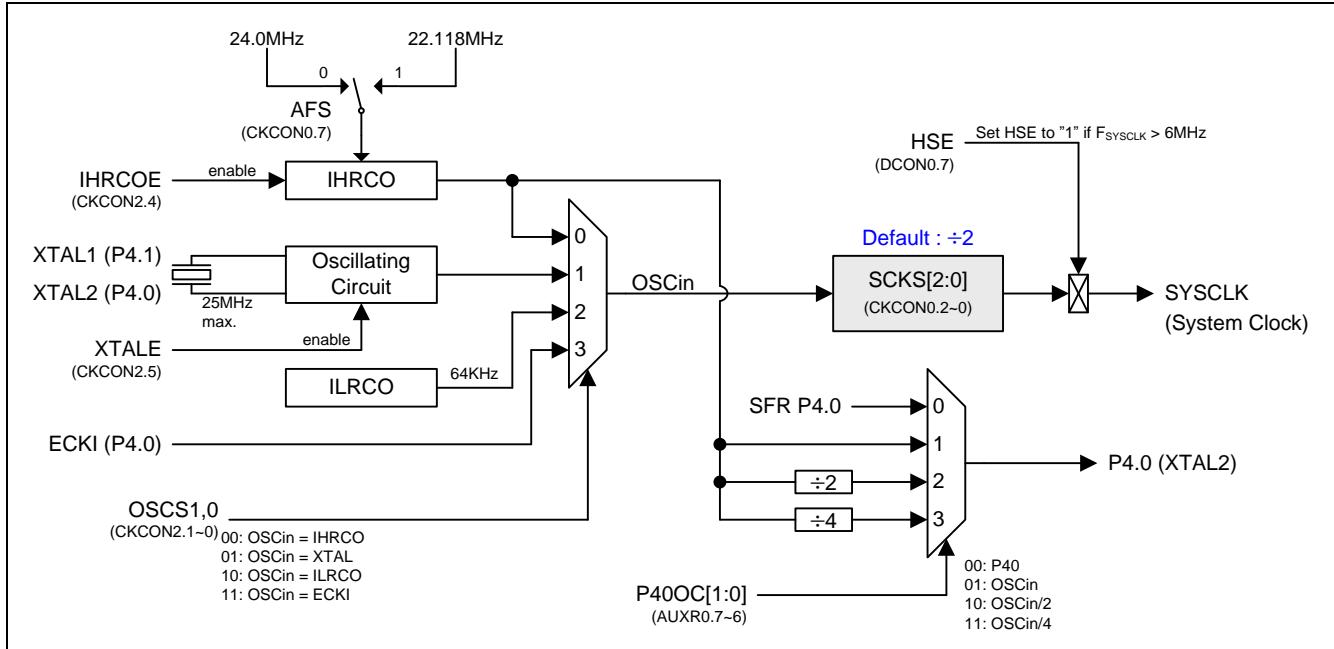

系统时钟有 4 个时钟源：内部快频 RC 震荡器（IHRCO），外部晶振，内部慢频 RC 震荡器（ILRCO）和外部频率输入。如图 9-1 所示 MA86E/L104 系统时钟结构。

MA86E/L104 默认值是 IHRCO 24.0MHz 2 分频作为系统时钟，并保留晶振脚 P4.0/P4.1 普通 I/O 口的特性。软件可以根据应用要求自由切换 4 种时钟的任意一种作为系统时钟，但必须等时钟稳定后才能切换。如果软件选择外部时钟模式，脚 P4.0 和 P4.1 分配给 XTAL2 和 XTAL1。并且 P4.0/P4.1 普通 I/O 功能失效。在外部时钟输入模式（ECKI），时钟源来自 P4.0，P4.1 仍然是普通 I/O 口。

软件可以选择 IHRCO 两种频率，另一种是 22.118MHz。通过软件设置位 AFS（CKCON0.7）来选择，两种 IHRCO 频率 22.118MHz 和 24.0MHz 都是高精度，在全工作电压和温度范围内频漂在  $\pm 4\%$  以内。在 IHRCO 或 ILRCO 模式，P4.0 可以作为全时钟（OSCin）输出或 2 分频时钟（OSCin/2）输出或 4 分频时钟（OSCin/4）输出给其他系统时钟源应用。

时钟分配器分配 4 种时钟源的一种为系统时钟 SYSCLK，如下图所示：图 8-1。用户能通过设置 SCKS2~SCKS0 位（CKCON0 寄存器）来获得理性的时钟。在上电复位后系统时钟的默认是 2 分频。

### 8.1. 时钟结构

图 8-1 显示了 MA86E/L104 的时钟系统。系统时钟可以于外部晶振或内部振荡作为来源。

图 8-1 系统时钟

## 8.2. 时钟寄存器

### CKCON0:时钟控制寄存器 0

SFR 页 = 普通 & P 页

SFR 地址 = 0xC7 复位值 = 0xxx-x001

| 7   | 6 | 5 | 4 | 3 | 2     | 1     | 0     |

|-----|---|---|---|---|-------|-------|-------|

| AFS | 0 | 0 | 0 | 0 | SCKS2 | SCKS1 | SCKS0 |

| R/W | W | W | W | W | R/W   | R/W   | R/W   |

Bit 7: AFS, 频率选择

0: 选择 IHRCO 输出 **24.0MHz**。

1: 选择 IHRCO 输出 **22.118MHz**。

Bit 6~3: 保留位。写 CKCON0 时, 这 4 个位必须写“0”。

Bit 2~0: SCKS2 ~ SCKS0, 系统时钟分频器选择位, SCKS[2:0] 缺损值 “001” 选择的系统时钟是 OSCin/2.

| SCKS[2:0] | System Clock |

|-----------|--------------|

| 0 0 0     | OSCin        |

| 0 0 1     | OSCin /2     |

| 0 1 0     | OSCin /4     |

| 0 1 1     | OSCin /8     |

| 1 0 0     | OSCin /16    |

| 1 0 1     | OSCin /32    |

| 1 1 0     | OSCin /64    |

| 1 1 1     | OSCin /128   |

### CKCON2:时钟控制寄存器 2

SFR Page = P

SFR 地址 = 0x40

复位值 = **0001-0000**

| 7 | 6 | 5     | 4      | 3 | 2 | 1     | 0     |

|---|---|-------|--------|---|---|-------|-------|

| 0 | 0 | XTALE | IHRCOE | 0 | 0 | OSCS1 | OSCS0 |

| W | W | R/W   | R/W    | W | W | R/W   | R/W   |

Bit 7~6: 保留位。写 CKCON0 时, 这 2 个位必须写“0”

Bit 5: XTALE, 外部晶振(XTAL) 使能。

0: 禁止 XTAL 震荡电路。在这种情况下, XTAL2 XTAL1 表现为 Port 4.0 Port 4.1.

1: 使能 XTAL 震荡电路。如果软件设置这个位, 必须等待 **3 ms** XTAL 才能稳定输出。

Bit 4: IHRCOE, 内部快频 RC 震荡使能位。默认设置为 MCU 时钟源

0: 禁止内部快频 RC 震荡电路。

1: 使能内部快频 RC 震荡电路。如果软件设置这个位, 必须等待 **32 us** IHRCO 才能稳定输出。

Bit 3~2: 保留位。写 CKCON0 时, 这 2 个位必须写“0”。

Bit 1~0: OSCS[1:0], OSCin 时钟选择。OSCin 缺损选项是 IHRCO.

| OSCS[1:0] | OSCin 时钟选择                  |

|-----------|-----------------------------|

| 0 0       | IHRCO                       |

| 0 1       | XTAL                        |

| 1 0       | ILRCO                       |

| 1 1       | ECKI, 外部时钟输入在 (P4.0) OSCin. |

### AUXR0: 辅助寄存器 0

SFR 地址 = 0xA1

复位值 = 000x-0000

| 7      | 6      | 5     | 4  | 3     | 2     | 1     | 0     |

|--------|--------|-------|----|-------|-------|-------|-------|

| P40OC1 | P40OC0 | P40FD | -- | P1FS1 | P1FS0 | INT1H | INT0H |

| R/W    | R/W    | R/W   | W  | R/W   | R/W   | R/W   | R/W   |

Bit 7~6: P40 输出配置控制位 1 和位 0, 这两位仅仅当内部 RC 震荡 (IHRCO 或 ILRCO) 被选择为系统时钟源时有效。这种情况, XTAL2 和 XTAL1 改变功能作 P4.0 和 P4.1。在外部时钟输入模式, P4.0 专用于时钟输入脚, 在内部震荡模式下, P4.0 为普通 I/O 或时钟源发生器提供下列选项, 当 P40OC[1:0] 索引为非 P4.0 GPIO 功能时, P4.0 将驱动内部振荡器 (IHRCO 或 ILRCO) 输出为其它设备提供时钟源。

| P40OC[1:0] | P4.0 功能 | P4.0 I/O 模式 |

|------------|---------|-------------|

| 00         | P40     | By P4M0.0   |

| 01         | OSCin   | By P4M0.0   |

| 10         | OSCin/2 | By P4M0.0   |

| 11         | OSCin/4 | By P4M0.0   |

当 P4.0 作为时钟输出功能, 设置 P4M0.0 为 “1” 选者 P4.0 为推挽输出

Bit 5: P40FD, P4.0 快速驱动标志。

0: P4.0 默认驱动输出

1: P4.0 快速驱动输出使能。若 P4.0 被配置为时钟输出, 当 P4.0 输出频率大于 12MHz (5V) 或者大于 6MHz (3V) 时使能此位。

### DCON0: 设备控制 0

SFR 页 = 仅 P 页

SFR 地址 = 0x4C

RESET = 1000-0010

| 7   | 6    | 5 | 4 | 3 | 2 | 1     | 0 |

|-----|------|---|---|---|---|-------|---|

| HSE | IAPO | 0 | 0 | 0 | 0 | RSTIO | 0 |

| W   | W    | W | W | W | W | W     | W |

Bit 7: HSE, 使能高速工作

0: 选择 MCU 在低速模式下运行, 降低内部电路的速度来减小功耗。

1: 如果  $F_{SYSCLK} > 6MHz$ , 置位使能 MCU 全速运行

### 8.3. 系统时钟示例代码

(1) 规定功能: IHRCO 从 24MHz 更改到 22.118MHz

汇编语言代码范例:

```

ORL CKCON0,#(AFS) ; 选择 IHRCO 输出 22.118MHz, AFS=0x80

```

C 语言代码范例:

```

CKCON0 |= AFS; //选择 IHRCO 输出 22.118MHz, AFS=0x80

```

(2). 规定功能: 系统时钟(SYSCLK)更改为 OSCin/1 (默认为 OSCin/2)

汇编语言代码范例:

```

ANL CKCON0,#(AFS) ; 设置 SCKS[2:0] = 0 来选择系统时钟(SYSCLK)为 OSCin/1

```

C 语言代码范例:

```

CKCON0 &= ~(SCKS2 | SCKS1 | SCKS0); //系统时钟(SYSCLK)为 OSCin/1

// SCKS[2:0], 系统时钟(SYSCLK)分频

// 0      | OSCin/1

// 1      | OSCin/2

// 2      | OSCin/4

// 3      | OSCin/8

// 4      | OSCin/16

// 5      | OSCin/32

// 6      | OSCin/64

// 7      | OSCin/128

```

(3). 规定功能: 当 MCU 使用 IHRCO 或 ILRCO 作为时钟源时, 选择外部晶振(XTAL)作为时钟源(OSCin) (默认为 IHRCO)

汇编语言代码范例:

```

MOV    IFADRL,#(CKCON2)          ; 索引 P 页地址为 CKCON2

CALL   _page_p_sfr_read         ; 读取 CKCON2 的数据

ORL    IFD,#(XTALE)             ; 使能外部晶振(XTALE)

;

CALL   _page_p_sfr_write        ; 写数据到 CKCON2,系统时钟(SYSCLK )必须小于 25MHz

check_XTOR:                   ; 检测外部晶振(XTAL)振荡准备好

MOV    A,AUXR1

JNB   ACC.4,check_XTOR        ; 等待 XTOR(AUXR1.4)为 1

ANL    IFD,#~(OSCS1 | OSCS0)    ; OSCin 时钟源更改为外部晶振(XTAL)

ORL    IFD,#(OSCS0)

CALL   _page_p_sfr_write        ; 写数据到 CKCON2

ANL    IFD,#~(IHRCOE)          ; 如果 MCU 从 IHRCO 更改之后禁止 IHRCO

CALL   _page_p_sfr_write        ; 写数据到 CKCON2

```

C 语言代码范例:

```

IFADRL = CKCON2;                //索引 P 页地址为 CKCON2

page_p_sfr_read();              //读取 CKCON2 的数据

IFD |=XTALE;                   //使能外部晶振(XTALE)

page_p_sfr_write ();           //写数据到 CKCON2,系统时钟(SYSCLK )必须小于 25MHz

while(AUXR1 & XTOR == 0x00);    //检测外部晶振(XTAL)振荡准备好

//等待 XTOR(AUXR1.4)为 1

IFD &= ~(OSCS1 | OSCS0);       // OSCin 时钟源更改为外部晶振(XTAL)

IFD |= OSCS0;

page_p_sfr_write ();           //写数据到 CKCON2

IFD &= ~IHRCOE;               //如果 MCU 从 IHRCO 更改之后禁止 IHRCO

page_p_sfr_write();            //写数据到 CKCON2

```

(4). 规定功能: 当 MCU 使用 IHRCO, ECKI 或 XTAL 作为时钟源时, 选择 ILRCO 作为时钟源(OSCin) (默认为 IHRCO)

汇编语言代码范例:

```

MOV    IFADRL,#(CKCON2)          ; 索引 P 页地址为 CKCON2

CALL   _page_p_sfr_read         ; 读取 CKCON2 的数据

ANL    IFD,#~(OSCS1 | OSCS0)    ; OSCin 时钟源更改为 ILRCO

ORL    IFD,#(OSCS1)

CALL   _page_p_sfr_write        ; 写数据到 CKCON2

ANL    IFD,#~(XTALE | IHRCOE)   ; 禁止 XTAL 和 IHRCO

CALL   _page_p_sfr_write        ; 写数据到 CKCON2

MOV    IFADRL,#(DCON0)          ; 索引 P 页地址为 DCON0

CALL   _page_p_sfr_read         ; 读取 DCON0 的数据

ANL    IFD,#~(HSE)              ; 当系统时钟(SYSCLK ≤ 6MHz)时为了省电禁止 HSE

CALL   _page_p_sfr_write        ; 写数据到 DCON0

```

C 语言代码范例:

```

IFADRL = CKCON2;                //索引 P 页地址为 CKCON2

page_p_sfr_read();               //读取 CKCON2 的数据

IFD = ~(OSCS1 | OSCS0);         // OSCin 时钟源更改为 ILRCO

IFD |= OSCS1;

page_p_sfr_write();              //写数据到 CKCON2

IFD &= ~(XTALE | IHRCOE);       //禁止 XTAL 和 IHRCO

page_p_sfr_write();              //写数据到 CKCON2

IFADRL = DCON0;                 //索引 P 页地址为 DCON0

page_p_sfr_read();               //读取 DCON0 的数据

IFD &= ~HSE;                     //当系统时钟(SYSCLK ≤ 6MHz)时为了省电禁止 HSE

```

|                     |              |

|---------------------|--------------|

| page_p_sfr_write(); | //写数据到 DCON0 |

|---------------------|--------------|

(5). 规定功能: 当 MCU 使用 IHRCO 或 ILRCO 作为时钟源时, 选择 ECKI 作为时钟源(OSCin) (默认为 IHRCO)

汇编语言代码范例:

|                                                                |  |

|----------------------------------------------------------------|--|

| MOV IFADRL,#(CKCON2); ; 索引 P 页地址为 CKCON2                       |  |

| CALL _page_p_sfr_read; ; 读取 CKCON2 的数据                         |  |

| ORL IFD,#(OSCS1   OSCS0); ; OSCin 时钟源更改为 ECKI                  |  |

| CALL _page_p_sfr_write; ; 写数据到 CKCON2, 系统时钟(SYSLCK) 必须小于 25MHz |  |

| ANL IFD,#~(XTALE   IHRCOE); ; 禁止 IHRCO 和 XTAL                  |  |

| CALL _page_p_sfr_write; ; 写数据到 CKCON2                          |  |

C 语言代码范例:

|                                                             |  |

|-------------------------------------------------------------|--|

| IFADRL = CKCON2; // 索引 P 页地址为 CKCON2                        |  |

| page_p_sfr_read(); // 读取 CKCON2 的数据                         |  |

| IFD  = OSCS1   OSCS0; // OSCin 时钟源更改为 ECKI                  |  |

| page_p_sfr_write(); // 写数据到 CKCON2, 系统时钟(SYSLCK) 必须小于 25MHz |  |

| IFD &= ~XTALE   IHRCOE; // 禁止 IHRCO 和 XTAL                  |  |

| page_p_sfr_write(); // 写数据到 CKCON2                          |  |

(6). 规定功能: 当 MCU 使用 ILRCO, ECKI 或 XTAL 作为时钟源时, 选择 IHRCO 作为时钟源(OSCin)

汇编语言代码范例:

|                                          |  |

|------------------------------------------|--|

| MOV IFADRL,#(CKCON2); ; 索引 P 页地址为 CKCON2 |  |

| CALL _page_p_sfr_read; ; 读取 CKCON2 的数据   |  |

| ORL IFD,#(IHRCOE); ; 使能 IHRCO            |  |

| CALL _page_p_sfr_write; ; 写数据到 CKCON2    |  |

| Delay_32us                               |  |

```

ANL    IFD,#~(OSCS1 | OSCS0)      ; OSCin 时钟源更改为 IHRCO

CALL   _page_p_sfr_write          ; 写数据到 CKCON2

```

```

ANL    IFD,#~(XTALE)             ; 禁止 XTAL

CALL   _page_p_sfr_write          ; 写数据到 CKCON2

```

C 语言代码范例：

```

IFADRL = CKCON2;                //索引 P 页地址为 CKCON2

page_p_sfr_read();              //读取 CKCON2 的数据

```

```

IFD |= IHRCOE;                  // 使能 IHRCO

page_p_sfr_write();              //写数据到 CKCON2

```

Delay 32us

```

IFD &= ~(OSCS1 | OSCS0);        // OSCin 时钟源更改为 IHRCO

page_p_sfr_write();              //写数据到 CKCON2

```

```

IFD &= ~ XTALE;                // 禁止 XTAL

page_p_sfr_write();              //写数据到 CKCON2

```

## (7). 规定功能: IHRCO 频率输出在 P4.0

汇编语言代码范例：

```

MOV    P4M0,#P4M00            ; 设置 P4.0 为推挽输出模式

ANL    AUXR0,#~(P40OC1|P40OC0) ; P4.0 更改为通用输入输出口(GPIO)功能

ORL    AUXR0,#(P40OC0|P4FD)    ; P4.0 = IHRCO 频率 + 引脚快速驱动

; P40OC[1:0]  |  P4.0

; 00       |  GPIO

; 01       |  IHRCO/1

; 10       |  IHRCO/2

; 11       |  IHRCO/4

```

C 语言代码范例:

```

P4M0 |= P4M00;          //设置 P4.0 为推挽输出模式

AUXR0 &= ~(P40OC0 | P40OC1);    // P4.0 更改为通用输入输出口(GPIO)功能

AUXR0 |= (P40OC0 | P4FD);      // P4.0 输出 IHRCO/1

//   AUXR0 = P40OC1|P4FD;        // P4.0 输出 IHROC/2

//   AUXR0 = P40OC1|P40OC0|P4FD; // P4.0 输出 IHRCO/4

```

## 9. 看门狗定时器 (WDT)

### 9.1. WDT 结构

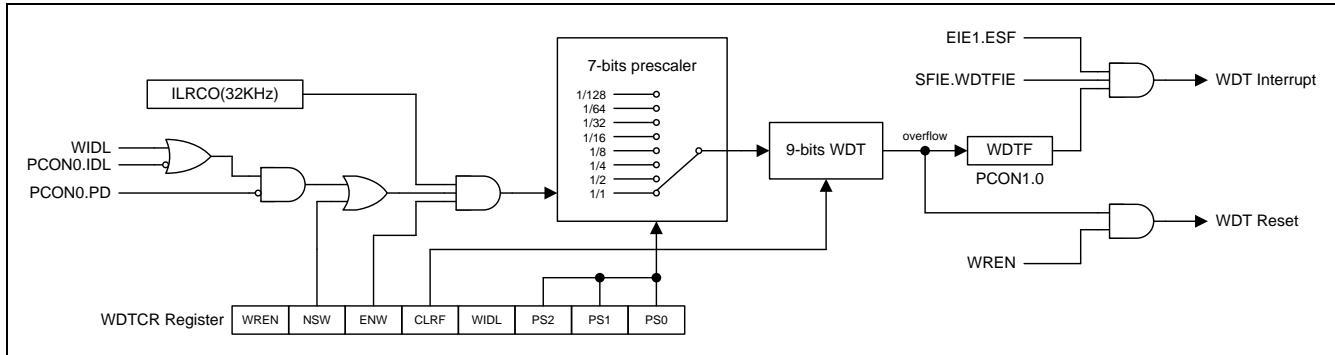

看门狗定时器 (WDT) 用来使程序从跑飞或死机状态恢复的一个手段。WDT 由一个 9 位独立定时器、一个 7 分频器和一个控制寄存器(WDTCR)组成。图 10-1 显示 MA86E/L104 WDT 结构框图。

当 WDT 使能，时钟源来自 32KHz ILRCO。WDT 溢出会设置位 WDTF PCON1.0，也能产生中断通过使能位 WDTFIE (SFIE.0) 和 ESF (EIE1.3)。溢出也能触发系统复位通过设置位 WREN (WDTCR.7)。软件可以在溢出之前在 CLRW 位 (WDTCR.4)上写“1”来清除它，可以阻止 WDT 溢出。

一旦 WDT 使能通过设置位 ENW，将没有办法使之失效除非上电复位或在 page-p SFR 覆盖 ENW，能清除位 ENW。WDTCR 会保持以前的值不会改变在硬件(RST-pin)复位、软件复位和 WDT 复位后。

WREN, NSW 和 ENW 都是一次性使能生效，写“1”使能。在 Page-P 中写“0”到位 WDTCR.7~5 禁止 WREN, NSW 和 ENW 使用。详见 WDT 章节和 P 页访问章节。

图 10-1 结构框图

### 9.2. WDT 在掉电模式和空闲模式期间

空闲模式，位标志 WIDL (WDTCR.3) 决定 WDT 是否计数。设置这个位能让 WDT 在空闲模式一直计数。如果硬件选项 WDTRCO 使能，WDT 会一直保持计数不管位 WIDL 设置情况。

掉电模式，ILRCO 不会停如果 NSW (WDTCR.6) 使能。这会让 WDT 保持计数即使掉电模式下(Watch 模式)。WDT 溢出后，软件能设置进入中断或复位 唤醒 CPU。

### 9.3. WDT 寄存器

**WDTCR: 控制寄存器**

SFR 地址 = 0xE1

POR = 0000-0111 (xxx0\_xxxx 硬件选项)

| 7    | 6   | 5   | 4    | 3    | 2   | 1   | 0   |

|------|-----|-----|------|------|-----|-----|-----|

| WREN | NSW | ENW | CLRW | WIDL | PS2 | PS1 | PS0 |

Bit 7: WREN, WDT 复位使能标志， 初始值随硬件选项 WRENO。

0: WDT 溢出不产生复位。 WDT 溢出标志 WDTF 可以供软件检测或触发中断。

1: WDT 溢出产生系统复位。 一旦 WREN 已经设置， 不能用软件在常规页中清除， 但在 **page P** 中， 软件能修改其值 “0” 或 “1”。

Bit 6: NSW. 不停止的 WDT 标志。 初始值随硬件选项 NSWDT.

0: WDT 停止计数 MCU 在掉电模式。

1: WDT 永远不会停止计数 MCU 在掉电模式或空闲模式。 一旦 NSW 已经设置， 不能用软件在常规页中清除， 但在 **page P** 中， 软件能修改其值 “0” 或 “1”。

Bit 5: ENW. 使能 WDT 标志。

0: 禁止 WDT 运行， 这个位仅仅能被 POR 清除。

1: 使能 WDT， 一旦 ENW 已经被设置， 不能用软件在常规页中清除， 但在 **page P** 中， 软件能修改其值 “0” 或 “1”。

Bit 4: CLRW. WDT 清零位。

0: 在 WDT 里写 “0” 到这位无效

1: 写 “1” 到这位将清零 9 位 WDT 计数器到 000H。注意这位没有必要写 “0” 去清除它。置位它将清除 WDT 重新计数。

Bit 3: WIDL. WDT 空闲模式控制。

0: WDT 停止计数 MCU 在空闲模式。

1: WDT 保持计数 MCU 在空闲模式。

Bit 2~0: PS2 ~ PS0, 选择分频器输出作 WDT 基础时钟输入（分频系数设置）

| PS[2:0] | 分频值 | WDT 时间  |

|---------|-----|---------|

| 0 0 0   | 1   | 15 ms   |

| 0 0 1   | 2   | 31 ms   |

| 0 1 0   | 4   | 62 ms   |

| 0 1 1   | 8   | 124 ms  |

| 1 0 0   | 16  | 248 ms  |

| 1 0 1   | 32  | 496 ms  |

| 1 1 0   | 64  | 992 ms  |

| 1 1 1   | 128 | 1.984 S |

**PCON1: 电源控制寄存器 1**

SFR 地址 = 0x97

上电复位值 = 00xx-0x00

| 7    | 6    | 5  | 4  | 3    | 2  | 1    | 0    |

|------|------|----|----|------|----|------|------|

| SWRF | EXRF | -- | -- | KBIF | -- | BOF0 | WDTF |

Bit 0: WDTF, WDT 溢出标志。

0: 必须由软件写“1”清除， 软件写“0”不操作。

1: 当 WDT 溢出时硬件置位此位，写“1”清除。

## 9.4. WDT 硬件选项

除了由软件初始化外，WDTCR 寄存器还能在上电的时候由硬件选项 WRENO,NSWDT,HWENW,HWWIDL 和 HWPS[2:0]来自动初始化，这些选项通过通用编程器来编程，如下所叙。

如果 HWENW 编程为“使能”，则硬件在上电时为 WDTCR 寄存器作如下的初始化工作：(1) ENWI 位置 1。 (2) 载入 WRENO 的值到 WREN 位。(3)载入 NSWDT 的值到 NSW 位。(4)载入 HWWIDL 的值到 WIDL 位。(5)载入 HWPS【2: 0】的值到 PS【2: 0】位。

如果 HWENW 和 WDSFWP 都被编程为“使能”，则硬件仍然会在上电时由 WDT 硬件选项初始化 WDTCR 寄存器的内容。之后，任何对 WDTCR 的位的写动作都会被忽略，除了写“1”到 WDTCR.4(CLRW)位来清 WDT 之外，即使通过对 Page-P SFR 的操作机制也不行。!

### **WRENO:**

使能：置位 WDTCR.WREN 以使能 WDTF 系统复位功能。

禁止：清除 WDTCR.WREN 以禁止 WDTF 系统复位功能。

### **NSWDT:**

使能：使能 WDT 在掉电模式也保持运行，设置位 WDTCR.NSW (watch 模式)。

禁止：禁止 WDT 在掉电模式下运行，清除位 WDTCR.NSW 。

### **HWWIDL, HWPS2, HWPS1, HWPS0:**

当 HWENW 被使能，上电复位时，这四个保险丝位将被载入到特殊功能寄存器 WDTCR 中。

### **HWENW:**

使能：上电时自动硬件使能看门狗定时器，并且自动加载 WRENO, NSWDT, HWWIDL 和 HWPS2~0 的值到 WDTCR 中。

禁止：上电时看门狗定时器（WDT）不自动使能。

### **WDSFWP: 禁止软件写 WDTCR 寄存器**

使能：特殊功能寄存器 WDTCR 软件写保护。

禁止：特殊功能寄存器 WDTCR 可被软件改写。

## 9.5. WDT 示例代码

(1) 规定功能: 使能 WDT 并且选择 WDT 周期为 248 毫秒(ms)

汇编语言代码范例:

```

ANL    PCON1,#(WDTF)          ; 清除 WDTF 标志(写“1”)

MOV    WDTCR,#(ENW | CLRW | PS2)   ; 使能 WDT 计数器并且设置 WDT 周期为 248 毫秒(ms)

```

C 语言代码范例:

```

PCON1 &= WDTF;                //清除 WDTF 标志(写“1”)

WDTCR = (ENW | CLRW | PS2);    //使能 WDT 计数器并且设置 WDT 周期为 248 毫秒(ms)

// PS[2:0] | WDT 周期选择

// 0   | 15ms

// 1   | 31ms

// 2   | 62ms

// 3   | 124ms

// 4   | 248ms

// 5   | 496ms

// 6   | 992ms

// 7   | 1.984s

```

(2) 规定功能: 如何禁止 WDT

汇编语言代码范例:

```

MOV    IFD,WDTCR            ; 读取 WDTCR 数据

ANL    IFD,#~(ENW)           ; 清除 ENW 而禁止 WDT

MOV    IFADRL,#(WDTCR_P)     ; 索引 P 页地址为 WDTCR_P

CALL   _page_p_sfr_write     ; 写数据到 WDTCR

```

C 语言代码范例:

```

IFD = WDTCR;                //读取 WDTCR 数据

```

```

IFD &= ~ENW;                                //清除 ENW 而禁止 WDT

IFADRL = WDTCR_P;                           //索引 P 页地址为 WDTCR_P

page_p_sfr_write();                         //写数据到 WDTCR

```

### (3). 规定功能: 使能 WDT 复位功能并且选择 WDT 周期为 62 毫秒(ms)

汇编语言代码范例:

```

ANL    PCON1,#(WDTF)          ; 清除 WDTF 标志(写“1”)

MOV    WDTCR,#(WREN | CLRW | PS1)  ; 使能 WDT 复位功能并且设置 WDT 周期为 62 毫秒(ms)

ORL    WDTCR,#(ENW)           ; 使能 WDT 计数器, WDT 运行

```

C 语言代码范例:

```

PCON1 &= WDTF;                      //清除 WDTF 标志(写“1”)

WDTCR = WREN | CLRW | PS1;          //使能 WDT 复位功能并且设置 WDT 周期为 62 毫秒(ms)

WDTCR |= ENW;                       //使能 WDT 计数器, WDT 运行

```

### (4). 规定功能: 使能 WDTCR 的写保护

汇编语言代码范例:

```

ANL    PCON1,#(WDTF)          ; 清除 WDTF 标志(写“1”)

MOV    WDTCR,#(ENW | CLRW | PS2)  ; 使能 WDT 计数器并且设置 WDT 周期为 248 毫秒(ms)

MOV    IFADRL,#(SPCON0)        ; 索引 P 页地址为 SPCON0

CALL   _page_p_sfr_read       ; 读取 SPCON0 数据

ORL    IFD,#(WRCTL)           ; 使能 WDTCR 的写保护

CALL   _page_p_sfr_write      ; 写数据到 SPCON0

MOV    IFD,WDTCR              ; 读取 WDTCR 数据

ORL    IFD,#(CLRW)            ; 使能 CLRW

```

|                        |                          |

|------------------------|--------------------------|

| MOV IFADRL,#(WDTCR_P)  | ; 索引 P 页地址为 WDTCR_P      |

| CALL _page_p_sfr_write | ; 写数据到 WDTCR 而清零 WDT 计数器 |

C 语言代码范例:

```

PCON1 &= WDTF;           //清除 WDTF 标志(写“1”)

WDTCR = ENW | CLRW | PS2; //使能 WDT 计数器并且设置 WDT 周期为 248 毫秒(ms)

IFADRL = SPCON0;          //索引 P 页地址为 SPCON0

page_p_sfr_read();        //读取 SPCON0 数据

IFD |= WRCTL;             //使能 WDTCR 的写保护

page_p_sfr_write();       // 写数据到 SPCON0

IFD = WDTCR;               //读取 WDTCR 数据

IFD |= CLRW;               // 使能 CLRW

IFADRL = WDTCR_P;          //索引 P 页地址为 WDTCR_P

page_p_sfr_write();        //写数据到 WDTCR 而清零 WDT 计数器

```

## 10. 系统复位

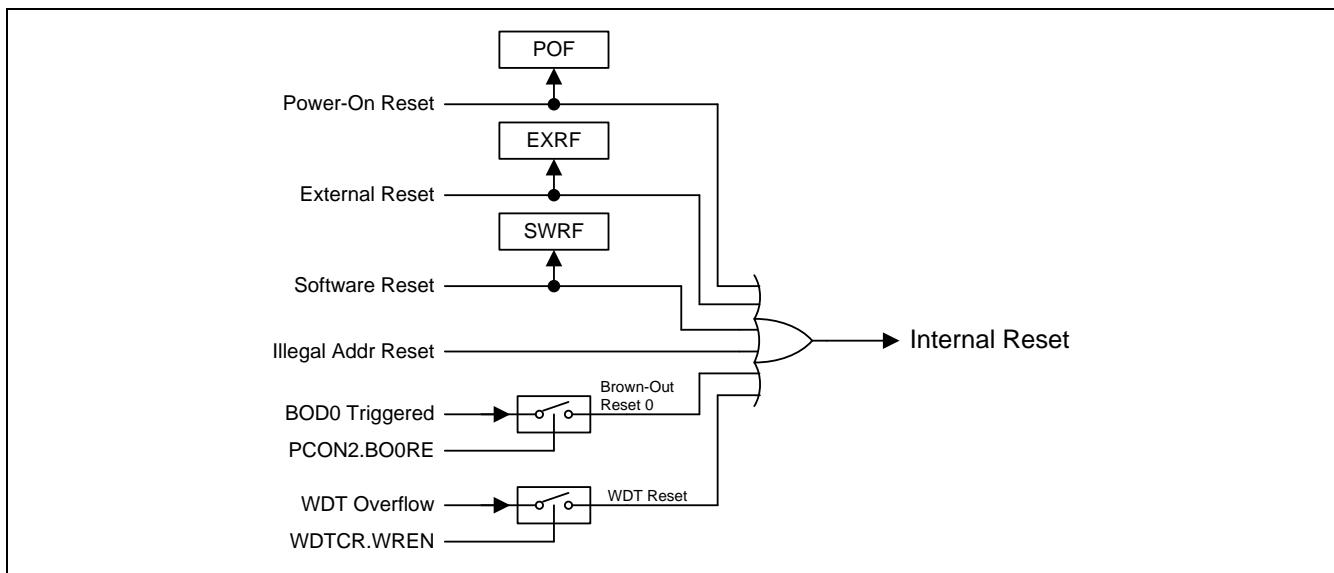

复位期间，所有的 I/O 寄存器都设置为初始值，程序会根据 OR 设置选择从复位向量的 0000H 开始运行，或者根据 OR 设置从 ISP 地址开始运行。The MA86E/L104 有 6 种复位源：上电复位，外部复位，软件复位，非法地址复位，WDT 复位和低电压复位。如图所示：图 11-1 系统复位源（MA86E/L104）。

下面的选项描述复位产生源及其相应的控制寄存器和指示标志。

### 10.1. 复位源

图 11-1 展示了 MA86E/L104 的复位系统，和所有复位源

图 11-1 系统复位源

### 10.2. 上电复位

上电复位 (POR) 用于在电源上电过程中产生一个复位信号。微控制器在 VDD 电压上升到  $V_{POR}$  (POR 开始电压) 电压之前将保持复位状态。VDD 电压降到  $V_{POR}$  之下后微控制器将再次进入复位状态。在一个电源周期中，如果需要再产生一次上电复位 VDD 必须降到  $V_{POR}$  之下。

#### PCON0: 电源控制寄存器 0

SFR 地址 = 0x87

$POR = 0001-0000$ , 复位值 = 000X-0000

| 7     | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-------|-----|-----|-----|-----|-----|-----|

| SMOD1 | SMOD0 | GF  | POF | GF1 | GF0 | PD  | IDL |

| R/W   | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

Bit 4: POF. Power-On 旗标。

0: 这标志必须通过软件清零以便认出下一个复位类型。

1: 当VDD从0 伏上升到正常电压时硬件复位，POF 也能有软件置位。

上电标志 POF 在上电过程中由硬件置“1”或当 VDD 电压降到 V<sub>POR</sub> 电压之下时由硬件置“1”。它能通过软件来清除但不受任何热复位（譬如：外部 RST 引脚复位、掉电检测器 Brown-Out 复位、软件(ISPCR.5)复位和 WDT 复位）的影响。它帮助用户检测 CPU 是否从上电开始运行。注意：POF 必须由软件清除。

#### **PCON1: 电源控制寄存器 1**

SFR 地址 = 0x97

POR = 00xx-0x00

| 7    | 6    | 5           | 4    | 3    | 2  | 1    | 0    |

|------|------|-------------|------|------|----|------|------|

| SWRF | EXRF | <b>POF1</b> | IARF | KBIF | -- | BOFO | WDTF |

| R/W  | R/W  | R/W         | R/W  | R/W  | W  | R/W  | R/W  |

Bit 4: POF1, 上电标志 1。是 POF 标志复制品，所以，这个标志 POF1 与 POF0 一样反应相同的电源状况。

0: 这位必须通过软件清零，写“1”清零，写“0”无效。

1: 当VDD 由0V上升到普通电压时，硬件置位此位，写“1”清零。

#### **10.3. 外部复位**

保持复位引脚 RST 至少 24 个振荡周期的高电平，将产生一个复位信号，为确保 MCU 正常工作，必须在 RET 引脚上连接可靠的硬件复位电路。

#### **PCON1: 电源控制寄存器 1**

SFR Address = 0x97

POR = 0010-0x00

| 7    | 6           | 5    | 4    | 3    | 2  | 1    | 0    |

|------|-------------|------|------|------|----|------|------|

| SWRF | <b>EXRF</b> | POF1 | IARF | KBIF | -- | BOFO | WDTF |

| R/W  | R/W         | R/W  | R/W  | R/W  | W  | R/W  | R/W  |

Bit 6: EXRF, 外部复位标志。

0: 这位必须通过软件清零，写“1”清零，写“0”无效。

1: 若外部复位产生则被硬件置位，写“1”清零。

#### **10.4. 软件复位**

软件通过对 SWRST(ISPCR.5) 位写“1”触发一个系统热复位，软件复位后，硬件置位 SWRF 标志(PCON1.7)。SWBS 标志决定 CPU 是从 ISP 还是 AP 区域开始运行程序。

#### **ISPCR: ISP 控制寄存器**

SFR Address = 0xE5

RESET = 0000-xxxx

| 7     | 6    | 5            | 4     | 3 | 2  | 1  | 0  |

|-------|------|--------------|-------|---|----|----|----|

| ISPEN | SWBS | <b>SWRST</b> | CFAIL | - | -- | -- | -- |

| R/W   | R/W  | R/W          | R/W   | W | W  | W  | W  |

Bit 6: SWBS, 软件引导控制

0: 用来选择软件复位后从 AP-空间。

1: 用来选择软件复位后从 ISP-空间。

Bit 5: SWRST, 软件复位触发控制

0: 无操作

1: 产生软件系统复位，它将被硬件自动清除。

#### **PCON1: 电源控制寄存器 1**

SFR 地址 = 0x97

POR = 0010-0x00

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

|             |      |      |      |      |    |      |      |

|-------------|------|------|------|------|----|------|------|

| <b>SWRF</b> | EXRF | POF1 | IARF | KBIF | -- | BOF0 | WDTF |

| R/W         | R/W  | R/W  | R/W  | R/W  | W  | R/W  | R/W  |

Bit 7: SWRF, 软件复位标志。

0: 这位必须通过软件清零，写“1”清零，写“0”无操作。

1: 软件复位产生时硬件置位此位，写“1”清零。

## 10.5. 掉电检测器（Brown-Out）复位

**MA86E/L104** 中，掉电检测器(BOD0)检测电源电压(VDD)，掉电检测器(BOD0)的检测固定点为 VDD=4.0V(E 系列) 2.6V(L 系列)，如果 VDD 电压低于 BOD0 检测点，则置位 BOF0 标志，如果 BOORE (PCON2.1) 被使能，BOD0 事件将触发一个 CPU 复位并置位 BOF0 指示一个掉点检测器 (BOD0) 复位发生。

### PCon1: 电源控制寄存器 1

SFR 地址 = 0x97

POR = 00xx-0x00

|      |      |    |    |      |    |             |      |

|------|------|----|----|------|----|-------------|------|

| 7    | 6    | 5  | 4  | 3    | 2  | 1           | 0    |

| SWRF | EXRF | -- | -- | KBIF | -- | <b>BOF0</b> | WDTF |

Bit 1: BOF0, BOFO 复位标志。

0: 这位必须通过软件清零，写“1”清零，写“0”无操作。

1: 当 VDD 电压碰到 BOD0 检测点时，硬件置位此位，写“1”清零。如果 BOORE (PCON2.1) 被使能，BOD0 事件将触发一个 CPU 复位并置位 BOF0 指示一个掉点检测器 (BOD0) 复位发生。

## 10.6. WDT 复位

当 WDT 使能开始计数，WDT 溢出时置位 WDTF 标志。如果 WREN (WDTCR.7) 使能，WDT 溢出将引起一个系统热复位，软件可以读 WDTF 标志来确认 WDT 复位发生。

### PCon1: 电源控制寄存器 1

SFR Address = 0x97

POR = 00xx-0x00

|      |      |    |    |      |    |      |      |

|------|------|----|----|------|----|------|------|

| 7    | 6    | 5  | 4  | 3    | 2  | 1    | 0    |

| SWRF | EXRF | -- | -- | KBIF | -- | BOF0 | WDTF |

Bit 0: WDTF, WDT 溢出/复位 标志。

0: 这位必须通过软件清零，写“1”清零，写“0”无操作。

1: 当 WDT 溢出产生时硬件置位此位，写“1”清零。如果位 WREN (WDTCR.7) 被设置，WDTF 标志指示一个 WDT 复位产生。

## 10.7. 非法地址复位

**MA86E/L104** 中，如果程序运行到非法地址诸如超过 ROM 限制程序地址时触发一个 CPU 热复位并置位 IARF (PCON1.4) 标志，以指示一个非法地址复位发生。

## 10.8. 复位示例代码

### (1) 规定功能: 触发一个软件复位

汇编语言代码范例:

```

ORL    ISPCR,#SWRST      ; 触发一个软件复位

```

C 语言代码范例:

```

ISPCR |= SWRST;          //触发一个软件复位

```

### (2). 规定功能: 使能 BOD0 复位

汇编语言代码范例:

```

MOV    IFADRL,#PCON2      ; 索引 P 页地址为 PCON2

CALL   _page_p_sfr_read  ; 读取 PCON2 数据

ORL    IFD,#BO0RE        ; 使能 BOD0 复位功能

CALL   _page_p_sfr_write ; 写数据到 PCON2

```

C 语言代码范例:

```

IFADRL = PCON2;           // 索引 P 页地址为 PCON2

page_p_sfr_read();        // 读取 PCON2 数据

IFD |= BO0RE;             //使能 BOD0 复位功能

page_p_sfr_write();       // 写数据到 PCON2

```

## 11. 电源管理

**MA86E/L104** 支持一个电源监测模块（掉电侦察器(BOD0)模块），和 6 种电源节能模式：空闲模式（IDLE）、掉电模式（Power-Down）、慢频模式、副频模式、Watch 模式、Monitor 模式。

通过 BOFO 标志位 BOD0 报告电源状态，软件可以通过这个状态产生中断或复位。6 种电源节能模式提供不同的节能应用，通过对 CKCON0, CKCON2, PCON0, PCON1, PCON2 和 WDTCR 寄存器的访问来操作这些电源事件。.

### 11.1. 电源监控模块

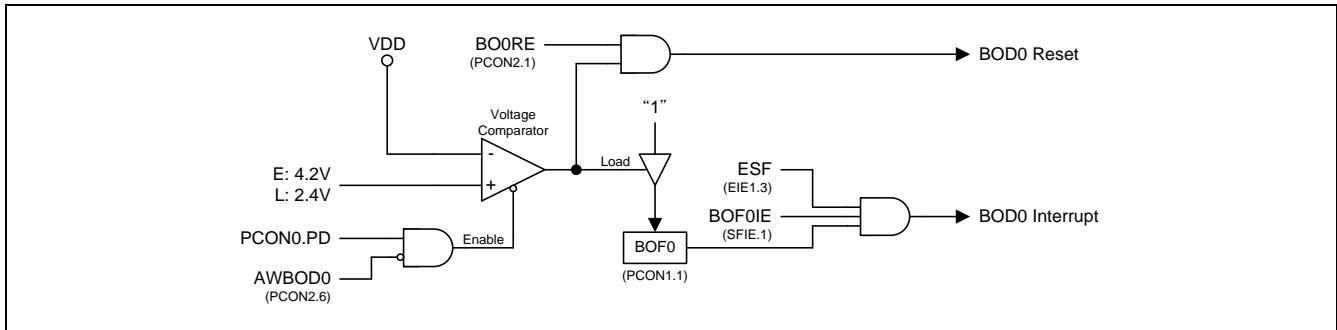

**IMA86E/L104**，有一个片上检测器 (BOD0) 通过比较固定的触发电压来检测芯片电压，图 12-1 是 BOD0 功能逻辑图，BOD0 检测固定触发电压为  $VDD=4.0V$ （**5V** 应用）和  $2.6V$  在（**3.3V** 应用）。当  $VDD$  降到触发电压以下时，BOFO (PCON1.1) 标志被置位，如果 ESF (EIE1.3) 和 BOFOIE (SFIE.1) 被使能，不管是普通模式或空闲模式都能产生一个中断请求以响应(BOD0)事件，如果 AWBOD0 (PCON2.6) 使能，这个中断也能唤醒掉电模式。

当 BOORE (PCON2.1) 被使能，BOD0 事件产生一个系统复位并硬件置位 BOFO 指示一个 BOD0 复位事件已经产生。在普通模式和空闲模式下 BOD0 事件能重新启动 CPU，如果 AWBOD0 (PCON2.6) 位被使能，也能重新启动掉电模式。

图 11-1 电源监控检测器

### 11.2. 电源节省模式

#### 11.2.1. 慢频模式

程序设置位 SCKS2~SCKS0( CKCON0 寄存器，参考系统时钟选项“[8 系统时钟](#)”为非 0/0/0 值，可以减慢 MCU 的工作速度达到节能的目的，使用者考量在特殊的程序段使用合适的慢速度，原则上不应该影响系统的其他功能。而且，应该在普通的程序段恢复到正常的速度。

#### 11.2.2. 副频模式

设置 OSCE1~0 选择 OSCE1~0 作为系统时钟，MCU 的工作频率会慢下来，32KHz ILRCO 系统频率使 MCU 工作在特别慢的速度和功耗下，另外设置 SCKS2~SCKS0 位 ( CKCON0 寄存器，参考系统时钟选项“[8 系统时钟](#)” ) 使用者可以使 MCU 的速度最低到 250HZ。

### 11.2.3. Watch 模式

如果看门狗被使能并且位被设置，看门狗在掉电模式保持运行，这个在 **MA86E/L104** 应用中叫 Watch 模式。当 When WDT 溢出，软件选择中断或系统复位来唤醒 CPU 并硬件置位 WDTF。通过定义 WDT 预分频最大唤醒时间能到 2 秒，更详细信息请参考“[9 看门狗定时器 \(WDT\)](#)”章节和“[13 中断](#)”章节。

### 11.2.4. Monitor 模式 (仅仅使用于 L-系列)

如果 AWBOD1 (PCON3.3) 被设置，即使在掉电模式下，掉电检测功能 BOD1 会有效，这就是 **MA86E/L104** 应用中的 Monitor 模式。当 BOD1 触发到检测电压，软件选择中断或系统复位来唤醒 CPU 并硬件置位 BOF1，更详细信息请参考“[11.1 电源监控模块](#)”和“[13 中断](#)”，这功能仅仅适用于 L-系列。

### 11.2.5. 空闲模式

可以通过软件的方式置 PCON.IDL 位，使设备进入空闲模式。在空闲模式下，系统不会给 CPU 提供时钟 CPU 状态、RAM、SP、PC、PSW、ACC 被保护起来。I/O 端口也保持当前的逻辑状态。空闲模式保持外部设置当有中断来时能唤醒 CPU，空闲模式下定时器 0、定时器 1、UART、KBI、BODO 仍然处于工作状态。在空闲模式下 WDT 唤醒 CPU 有条件制约。任何使能的中断源或复位都能终止空闲模式，一个中断会退出空闲模式，并同时进入中断服务程序，只有在中断返回后才会开始执行进入空闲模式指令之后的程序。

### 11.2.6. 掉电模式

可以通过软件的方法置位 PCON.PD 使设备进入掉电模式，掉电模式下，震荡器停止震荡，Flash 存储器掉电以节约电能，只有上电电路继续刷新电源，在减少 VDD 的时候 RAM 的内容仍然会被保持；但如果电源电压低于芯片工作电压，特殊功能寄存器 SFR 的内容就不一定能保持住。外部复位、上电复位、外部中断、使能的 KBI 使能的 BODO 或使能的没有停止的 WDT 能是系统推出掉电模式。

如果有下列情况发生，使用者至少要等 4 微秒后才能进入或再次进入掉电模式：刚开始运行代码(任何形式的复位后面)，或者刚刚退出掉电模式。为了在掉电模式达到最小功耗，软件必须设置所有的 I/O 为悬浮状态，包含封装中没有漏出来的 I/O。例如：**P1.7~P1.0 和 P4.1~P4.0 在 MA86E/L104AE8 (SOP8) 的封装中都没有秀出来**，软件必须设置 **P1/P4 SFR 控制位为 “0” (输出低)** 来避免脚位在掉电模式中处于悬浮状态。

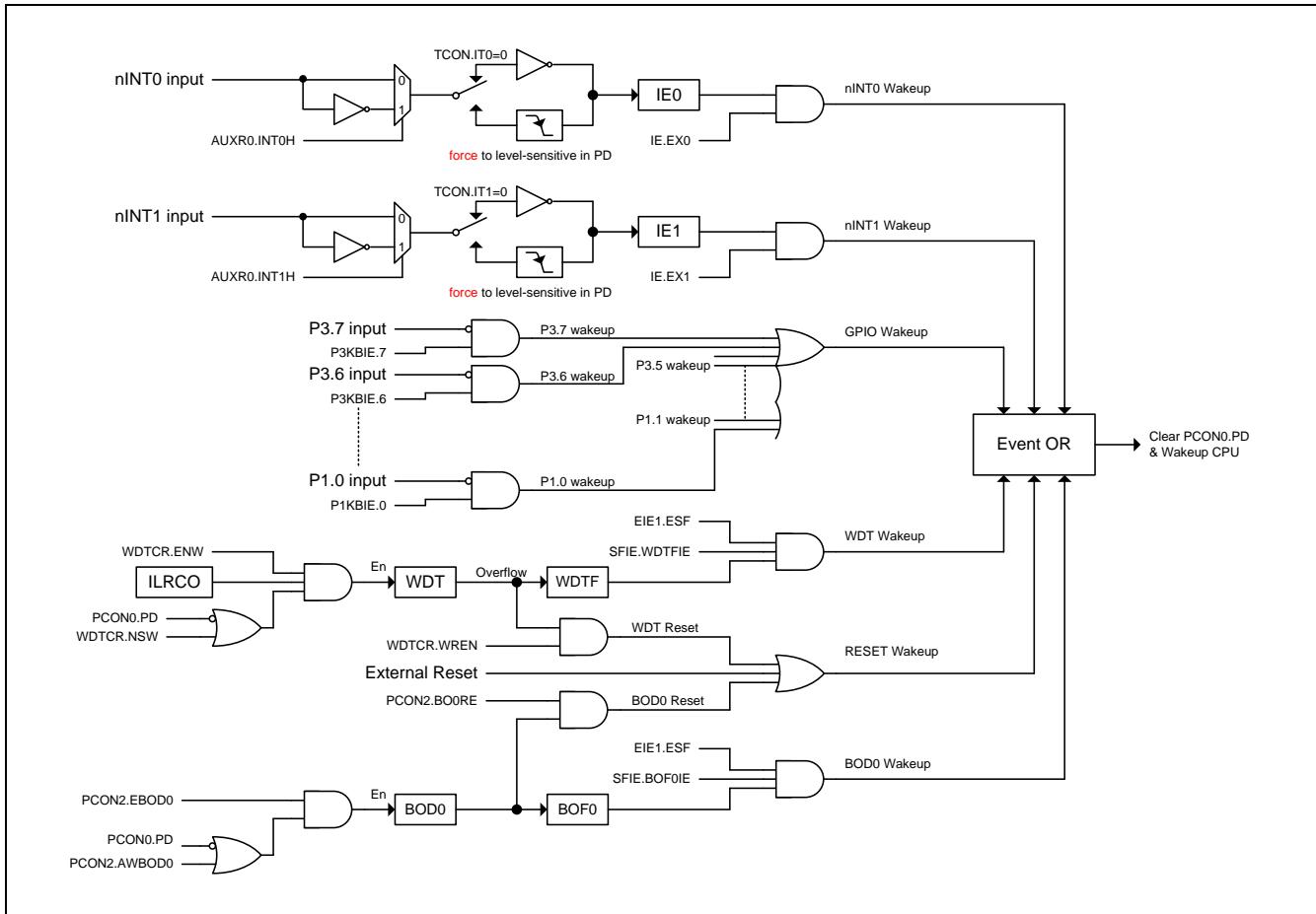

图 11-2 掉电唤醒结构标示了 MA86E/L104 在掉电模式中唤醒的进程。

图 11-2 掉电唤醒结构

### 11.2.7. 中断唤醒掉电模式

两个外部中断都能终止掉电模式，外部中断 nINT0 (P3.2), nINT1 (P3.3) 能退出掉电模式，为了能唤醒掉电模式，中断 nINT0, nINT1 必须使能并且设置为电平触发操作，如果外部中断使能且设置是边沿触发（上升或下降），他们会被硬件强置为电平触发（低电平或高电平）。

一个中断终止掉电模式，唤醒时间取决于内部定时。当中断口产生下降沿时，掉电模式被终止，震荡重新启动，并且一个内部计数器开始计数，在内部计数器没有计满之前内部时钟不允许被应用 CPU 也不能运行指令。计数溢出后，中断服务程序开始工作，为了避免中断被重复触发，中断服务程序在返回前应该被禁止，中断口低电平应保持足够长的时间以等待系统问题。

### 11.2.8. 复位唤醒掉电模式

如果 P3.6 设置为 RST 脚，RST 脚唤醒有点类似于中断，复位脚有上升沿电平时系统退出掉电模式，震荡重新启动，且一个内部计数器开始计数，在内部计数器没有计满之前内部时钟不允许被应用 CPU 也不能运行指令。复位脚必须保持足够长的高电平以保证系统完全复位，复位脚变低电平时开始执行程序。

值得注意的是当空闲模式被硬件复位唤醒时，前两个机器周期（内部复位没有取得控制权）程序正常从进入 IDLE 模式的后一条指令执行，这时内部硬件是禁止访问内部 RAM 的，但访问 I/O 端口没有被禁止，为了保证不可预料的写 I/O 口，在进入 IDLE 指令后不要放置写 I/O 口或外部存储器的指令（最好加两到三个 NOP 指令）。

### 11.2.9. KBI 键盘唤醒掉电模式

**MA86E/L104** 的键盘中断，P1.7 ~ P1.0, P3.7~P3.4, **P41, P40, P31** 和 P30 具有唤醒能力，可以通过 KBI 模块的控制寄存器 P1KBIE 、 P3KBIE ， P3.2/nINT0 、 P3.3/nINT1 进行使能。

通过使能 KBI 唤醒掉电模式有点类似中断唤醒，当使能 KBI 的 IO 口有低电平时系统退出掉电模式，震荡重新启动，且一个内部计数器开始计数，在内部计数器没有计满之前内部时钟不允许被应用 CPU 也不能运行指令。计数溢出后，CPU 响应 KBI 中断并入中断服务程序，细节请参考“16 键盘中断(KBI)”。

### 11.3. 电源控制寄存器

#### PCON0: 电源控制寄存器 0

SFR 地址 = 0x87

POR = 00xx-0x00

| 7     | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-------|-----|-----|-----|-----|-----|-----|

| SMOD1 | SMOD0 | --  | POF | GF1 | GF0 | PD  | IDL |

| R/W   | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

Bit 4: POF, 上电标志。

0: 这位必须由软件清零, 写“1”清零。

1: 当上电复位产生时硬件置位此位。

Bit 1: PD, 掉电控制位。

0: 软件清零或任何一个退出掉电模式的事件发生时硬件清零。

1: 置位则激活掉电操作（即进入掉电模式）。

Bit 0: IDL, 空闲模式控制位。

0: 软件清零或任何一个退出空闲模式的事件发生时硬件清零。

1: 置位则激活空闲操作（即进入空闲模式）。

#### PCON1: 电源控制寄存器 1

SFR 地址 = 0x97

POR = 0010-0x00

| 7    | 6    | 5  | 4  | 3    | 2  | 1    | 0    |

|------|------|----|----|------|----|------|------|

| SWRF | EXRF | -- | -- | KBIF | -- | BOF0 | WDTF |

| R/W  | R/W  | W  | W  | R/W  | W  | R/W  | R/W  |

Bit 7: SWRF, 软件复位标志。

0: 这位必须由软件清零, 写“1”清零。

1: 当软件复位产生时硬件置位此位。

Bit 6: EXRF, 外部复位标志。

0: 这位必须由软件清零, 写“1”清零。

1: 当外部复位产生时硬件置位此位。

Bit 5~4: 保留. 当写 PCON1 时, 软件必须在这些位上写“0”

Bit 3: KBIF 键盘中断标志。

0: 这位必须由软件清零, 写“1”清零。

1: 当键盘中断复位产生时硬件置位此位。

Bit 2: 保留当写 PCON1 寄存器时此位必须填“0”。

Bit 1: BOF0, Brown-Out 借察标志 0.

0: 这位必须由软件清零, 写“1”清零。

1: 当电源监控复位产生时硬件置位此位(E: 4.2V, L: 2.4V)。

Bit 0: WDTF, WDT 溢出标志

0: 这位必须由软件清零, 写“1”清零。

1: 当 WDT 复位产生时硬件置位此位。

### **PCon2: 电源控制寄存器 2**

SFR Page = P Only

SFR 地址 = 0x44

POR = x0xx-xx01

|    |               |    |    |    |    |       |   |

|----|---------------|----|----|----|----|-------|---|

| 7  | 6             | 5  | 4  | 3  | 2  | 1     | 0 |

| -- | <b>AWBODO</b> | -- | -- | -- | -- | BOORE | 1 |

W            W            W            W            W            W            W            W

Bit 7: 保留,写 PCON2 寄存器时此位必须填“0”。

Bit 6: AWBODO, 在掉电模式下 (PD) 使能电源监控模式 (BOD0) 控制位。

0: 电源监控模式 (BOD0) 在掉电模式下失效。

1: 电源监控模式 (BOD0) 在掉电模式下有效。

Bit 5~2: 保留,写 PCON2 寄存器时此几位必须填“0”。

Bit 1: BOORE, BOD0 复位使能标志, 初始为 OR1.BOORE 取反值。

0: 当 BOFO 已经设置, 禁止电源监控 (BOD0) 系统复位。

1: 当 BOFO 已经设置, 使能电源监控 (BOD0) 系统复位 (VDD 触到 4.0V(E) 或 2.6V(L))。

Bit 0: 保留给测试用, 写 PCON2 寄存器时此位必须填“1”。

### **P1KBIE: Port 1 KBI 使能控制寄存器**

SFR 地址 = 0xD7

RESET = 0000-0000

|         |         |         |         |         |         |         |         |

|---------|---------|---------|---------|---------|---------|---------|---------|

| 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

| P17KBIE | P16KBIE | P15KBIE | P14KBIE | P13KBIE | P12KBIE | P11KBIE | P10KBIE |

R/W            R/W            R/W            R/W            R/W            R/W            R/W            R/W

Bit 7~0: 每个 P1 引脚键盘输入功能使能控制位。

0: 相对应的引脚键盘输入功能失效

1: 相对应的引脚键盘输入功能使能, 低电压触发。

### **P3KBIE: Port 3 KBI 使能控制寄存器**

SFR 地址 = 0xD6

RESET = 0000-0000

|         |         |         |         |                |                |         |         |

|---------|---------|---------|---------|----------------|----------------|---------|---------|

| 7       | 6       | 5       | 4       | 3              | 2              | 1       | 0       |

| P37KBIE | P36KBIE | P35KBIE | P34KBIE | <b>P41KBIE</b> | <b>P40KBIE</b> | P31KBIE | P30KBIE |

R/W            R/W            R/W            R/W            R/W            R/W            R/W            R/W

Bit 7~0: P3.7 ~ P3.4, P4.1, P4.0, P3.1 和 P3.0 引脚键盘输入功能使能控制位。

0: 相对应的引脚键盘输入功能禁止

1: 相对应的引脚键盘输入功能使能, 低电压触发。

## 11.4. 电源控制示例代码

(1) 规定功能: 选择系统时钟分频为 OSCin/128 的低速模式 (默认为 OSCin/2)

汇编语言代码范例:

```

ORL    CKCON0,#(SCKS0 | SCKS1 | SCKS2) ; 选择系统时钟分频为 OSCin/128

MOV    IFADRL,#DCON0           ; 索引 P 页地址为 DCON0

CALL   _page_p_sfr_read       ; 读取 DCON0 数据

ANL    IFD,#~(HSE)            ; 当系统时钟 SYSCLK ≤ 6MHz 为了省电禁止 HSE

CALL   _page_p_sfr_write      ; 写数据到 DCON0

```

C 语言代码范例:

```

CKCON0 |= (SCKS2 | SCKS1 | SCKS0); //选择系统时钟分频为 OSCin/128.

IFADRL = DCON0;                  // 索引 P 页地址为 DCON0

page_p_sfr_read();               // 读取 DCON0 数据.

IFD &= ~HSE;                    //当系统时钟 SYSCLK ≤ 6MHz 为了省电禁止 HSE

page_p_sfr_write();              // 写数据到 DCON0

```

(2) 规定功能: 选择系统时钟分频为 OSCin/2 的副频模式 (默认为 OSCin/2=32KHz/2=16KHz)

汇编语言代码范例:

```

MOV    IFADRL,#CKCON2          ; 索引 P 页地址为 CKCON2

CALL   _page_p_sfr_read        ; 读取 CKCON2 数据

ANL    IFD,#~(OSCS1|OSCS0)     ; OSCin 时钟源更改为 ILRCO

ORL    IFD,#OSCS1

CALL   _page_p_sfr_write       ; 写数据到 CKCON2

```

```

ANL    IFD,#~(IHRCOE|XTALE)      ; 禁止 IHRCO 和 XTAL

CALL   _page_p_sfr_write         ; 写数据到 CKCON2

MOV    IFADRL,#DCON0            ; 索引 P 页地址为 DCON0

CALL   _page_p_sfr_read          ; 读取 DCON0 数据

ANL    IFD,#~(HSE)              ; 当系统时钟 SYSCLK ≤ 6MHz 为了省电禁止 HSE

CALL   _page_p_sfr_write         ; 写数据到 DCON0

MOV    A,CKCON0                ; 选择系统时钟为 OSCin/2

ANL    A,#~(SCKS2|SCKS1|SCKS0)

ORL    A,#SCKS0

MOV    CKCON0,A

```

#### C 语言代码范例:

```

IFADRL = CKCON2;                      // 索引 P 页地址为 CKCON2

page_p_sfr_read();                    // 读取 CKCON2 数据

IFD &= ~(OSCS1 | OSCS0);             // OSCin 时钟源更改为 ILRCO

IFD |= OSCS1;

page_p_sfr_write();                  // 写数据到 CKCON2

IFD = IFD & ~(IHRCOE|XTALE);        // 禁止 IHRCO 和 XTAL

page_p_sfr_write();                  // 写数据到 CKCON2

IFADRL = DCON0;                      // 索引 P 页地址为 DCON0

page_p_sfr_read();                   // 读取 DCON0 数据

IFD = IFD & ~(HSE);                 // 当系统时钟 SYSCLK ≤ 6MHz 为了省电禁止 HSE

page_p_sfr_write();                  // 写数据到 DCON0

ACC = CKCON0;                        // 选择系统时钟为 OSCin/2

ACC &= ~(SCKS2 | SCKS1 | SCKS0);

ACC |= SCKS0;

CKCON0 = ACC;

```

### (3). 规定功能: 现在 MCU 运行在外部振荡( XTAL)模式

汇编语言代码范例:

```

MOV    IFADRL,#CKCON2          ; 索引 P 页地址为 CKCON2

CALL   _page_p_sfr_read        ; 读取 CKCON2 数据

ORL    IFD,#(XTALE)            ; 使能外部振荡(XTAL)振荡

CALL   _page_p_sfr_write       ; 写数据到 CKCON2

check_XTOR_0:                  ; 检测外部振荡(XTAL)振荡准备好

MOV    A,AUXR1

JNB   ACC.4,check_XTOR_0      ; 等待 XTOR(AUXR1.4)为 1

ANL    IFD,#~(OSCS1|OSCS0)     ; OSCin 时钟源更改为外部振荡(XTAL)

ORL    IFD,#OSCS0

CALL   _page_p_sfr_write       ; 写数据到 CKCON2

ANL    IFD,#~(IHRCOE)          ; 如果 MCU 从 IHRCO 切换过来则禁止 IHRCO

CALL   _page_p_sfr_write       ; 写数据到 CKCON2

MOV    IFADRL,#DCON0           ; 索引 P 页地址为 DCON0

CALL   _page_p_sfr_read        ; 读取 DCON0 数据

ANL    IFD,#~(HSE)              ; 当系统时钟 SYSCLK ≤ 6MHz 为了省电禁止 HSE

CALL   _page_p_sfr_write       ; 写数据到 DCON0

ANL    CKCON0,#~(SCKS2|SCKS1|SCKS0); 系统时钟 SYSCLK = OSCin/1

```

C 语言代码范例:

```

IFADRL = CKCON2;             // 索引 P 页地址为 CKCON2

page_p_sfr_read();            // 读取 CKCON2 数据

IFD |= XTALE;                 //使能外部振荡(XTAL)振荡

page_p_sfr_write();           // 写数据到 CKCON2

```

```

while( AUXR1&XTOR == 0x00 );           //检测外部振荡(XTAL)振荡准备好

//等待 XTOR(AUXR1.4)为 1

IFD &= ~(OSCS1 | OSCS0);             // OSCin 时钟源更改为外部振荡(XTAL)

IFD |= OSCS0;

page_p_sfr_write();                  // 写数据到 CKCON2

IFD &= ~IHRCOE;                    // 如果 MCU 从 IHRCO 切换过来则禁止 IHRCO

page_p_sfr_write();                 // 写数据到 CKCON2.

IFADRL = DCON0;                   // 索引 P 页地址为 DCON0

page_p_sfr_read();                 // 读取 DCON0 数据.

IFD &= ~HSE;                      //当系统时钟 SYSCLK ≤ 6MHz 为了省电禁止 HSE

page_p_sfr_write();                 // 写数据到 DCON0

CKCON0 &= ~(SCKS2 | SCKS1 | SCKS0); // 系统时钟 SYSCLK = OSCin/1

```

#### (4). 规定功能: 使能 2 秒(s)周期的 Watch 模式

汇编语言代码范例:

```

ORG      0003Bh

SystemFlag_ISR:

ANL      PCON1,#(WDTF)          ; 清除 WDT 标志(写“1”)

RETI

main:

ANL      PCON1,#WDTF          ; 清除 WDT 标志 (写“1”)

ORL      WDTCR,#(NSW|ENW|PS2|PS1|PS0)

;使能 WDT 和 NSW (对 watch 模式)

;设置 PS[2:0] = 7 来选择 WDT 周期为 1.984 秒(s)

ORL      SFIE,#WDTFIE         ; 使能 WDT 中断

ORL      EIE1,#ESF             ; 使能系统标志中断

SETB    EA                     ; 使能全局中断

```

```

ORL PCON0,#PD ; 设置 MCU 为掉电模式

```

; MCU 等待唤醒

C 语言代码范例:

```

void SystemFlag_ISR (void) interrupt 7

{

PCON1 &= WDTF; //清除 WDT 标志(写“1”)

}

void main (void)

{

PCON1 &= WDTF; //清除 WDT 标志 (写“1”)

WDTCR |= (NSW | ENW | PS2 | PS1 | PS0); //使能 WDT 和 NSW (对 watch 模式)

//设置 PS[2:0] = 7 来选择 WDT 周期为 1.984 秒(s)

SFIE |= WDTFIE; //使能 WDT 中断

EIE1 |= ESF; //使能系统标志中断

EA = 1; //使能全局中断

PCON0 |= PD; //设置 MCU 为掉电模式

// MCU 等待唤醒

}

```

#### (5). 规定功能: Monitor 模式 (仅 L-系列)

汇编语言代码范例:

```

ORG 0003Bh

```

SystemFlag\_ISR:

```

ANL PCON1,#(BOF0) ; 清除 BOD0 标志(写“1”)

```

```

RETI

```

main:

```

MOV IFADRL,#PCON2 ; 索引 P 页地址为 PCON2

```

```

CALL  _page_p_sfr_read           ; 读取 PCON2 数据

ORL    IFD,#AWBODO             ; 在掉电模式使能 BOD0 工作

CALL  _page_p_sfr_write         ; 写数据到 PCON2

ORL    SFIE,#BOF0IE            ; 使能 BOF0 中断

ORL    EIE1,#ESF                ; 使能系统标志中断

SETB   EA                      ; 使能全局中断

ORL    PCON0,#PD               ; 设置 MCU 为掉电模式

;   MCU 等待唤醒

```

#### C 语言代码范例:

```

void SystemFlag_ISR() interrupt 7

{

PCON1 &= BOF0;                  // 清除 BOD0 标志(写“1”)

}

void main()

{

IFADRL = PCON2;                // 索引 P 页地址为 PCON2

page_p_sfr_read();              // 读取 PCON2 数据

IFD |= AWBODO;                 //在掉电模式使能 BOD0 工作

page_p_sfr_write();             // 写数据到 PCON2

SFIE |= BOF0IE;                //使能 BOF0 中断

EIE1 |= ESF;                   //使能系统标志中断

EA = 1;                        //使能全局中断

PCON0 |= PD;                   //设置 MCU 为掉电模式

//   MCU 等待唤醒

```

}

#### (6). 规定功能:外部晶振 (XTAL)在掉电模式下安全并且快速唤醒

汇编语言代码范例:

```

MOV    IFADRL,#CKCON2          ; 索引 P 页地址为 CKCON2

CALL   _page_p_sfr_read        ; 读取 CKCON2 数据

ORL    IFD,#IHRCOE            ; 使能 IHRCO

CALL   _page_p_sfr_write       ; 写数据到 CKCON2

Delay_32us

ANL    IFD,#~(OSCS1|OSCS0)      ; OSCin 时钟源更改到 IHRCO

CALL   _page_p_sfr_write       ; 写数据到 CKCON2

ORL    PCON0,#PD              ; 设置 MCU 为掉电

; MCU 等待唤醒

check_XTOR:                   ; 检测外部振荡(XTAL)振荡准备好

MOV    A,AUXR1

JNB   ACC.4,check_XTOR        ; 等待 XTOR(AUXR1.4)为 1

ANL    IFD,#~(OSCS1 | OSCS0)    ; OSCin 时钟源更改为外部振荡(XTAL)

ORL    IFD,#(OSCS0)

CALL   _page_p_sfr_write       ; 写数据到 CKCON2

ANL    IFD,#~(IHRCOE)          ; 如果 MCU 从 IHRCO 切换过来则禁止 IHRCO

CALL   _page_p_sfr_write       ; 写数据到 CKCON2

```

C 语言代码范例:

```

IFADRL = CKCON2;           // 索引 P 页地址为 CKCON2

page_p_sfr_read();          // 读取 CKCON2 数据

```

```

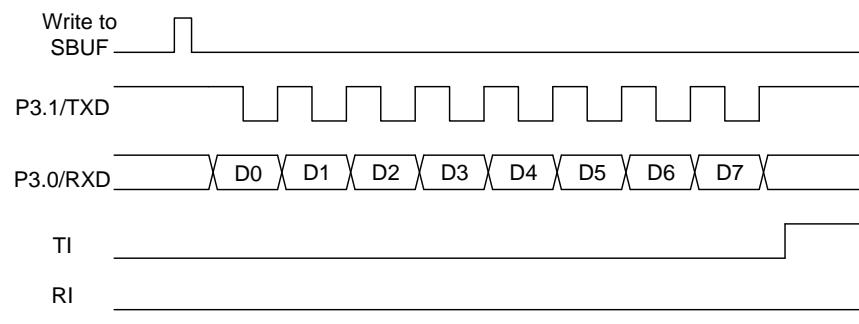

IFD |= IHRCOE;           // 使能 IHRCO